## PSoC 3, PSoC 5 TRM

# PSoC<sup>®</sup> 3, PSoC<sup>®</sup> 5 Architecture TRM

(Technical Reference Manual)

Document No. 001-50235 Rev. \*E

December 23, 2010

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

Copyright © 2008–2010 Cypress Semiconductor Corporation. All rights reserved.

PSoC and CapSense are registered trademarks of Cypress Semiconductor Corporation. PSoC Designer is a trademark of Cypress Semiconductor Corporation. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Purchase of I<sup>2</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name, NXP Semiconductors.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied, or reproduced for commercial use, in any form or by any means without the prior written consent of Cypress. Made in the U.S.A.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

#### Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress PSoC Datasheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# **Contents Overview**

| Section A: | Ove | erview                                    | 21  |

|------------|-----|-------------------------------------------|-----|

|            | 1.  | Introduction                              | 23  |

|            | 2.  | Getting Started                           | 29  |

|            | 3.  | Document Construction                     | 31  |

| Section B: | CPU | J System                                  | 35  |

|            | 4.  | 8051 Core                                 | 37  |

|            | 5.  | Cortex™-M3 Microcontroller                | 67  |

|            | 6.  | PSoC 3 Cache Controller                   | 81  |

|            | 7.  | PSoC 5 Cache Controller                   | 87  |

|            | 8.  | PHUB and DMAC                             | 91  |

|            | 9.  | Interrupt Controller                      | 107 |

| Section C: | Mer | mory                                      | 119 |

|            | 10. | Nonvolatile Latch                         | 121 |

|            | 11. | SRAM                                      | 125 |

|            | 12. | Flash Program Memory                      | 129 |

|            | 13. | EEPROM                                    | 131 |

|            | 14. | EMIF                                      | 133 |

|            | 15. | Memory Map                                | 141 |

| Section D: | Sys | stem Wide Resources                       | 145 |

|            | 16. | Clocking System                           | 147 |

|            | 17. | Power Supply and Monitoring               | 163 |

|            | 18. | Low Power Modes                           | 169 |

|            | 19. | Watchdog Timer                            | 175 |

|            | 20. | Reset                                     | 179 |

|            | 21. | I/O System                                | 187 |

|            | 22. | Flash, Configuration Protection           | 205 |

| Section E: | Dig | ital System                               | 211 |

|            | 23. | Universal Digital Blocks (UDBs)           | 213 |

|            | 24. | UDB Array and Digital System Interconnect | 255 |

|            | 25. | Controller Area Network (CAN)             | 263 |

|            | 26. | USB                                       | 279 |

|            | 27. | Timer, Counter, and PWM                   | 295 |

|            | 28. | I <sup>2</sup> C                      | 311 |

|------------|-----|---------------------------------------|-----|

|            | 29. | Digital Filter Block (DFB)            | 327 |

| Section F: | Ana | log System                            | 343 |

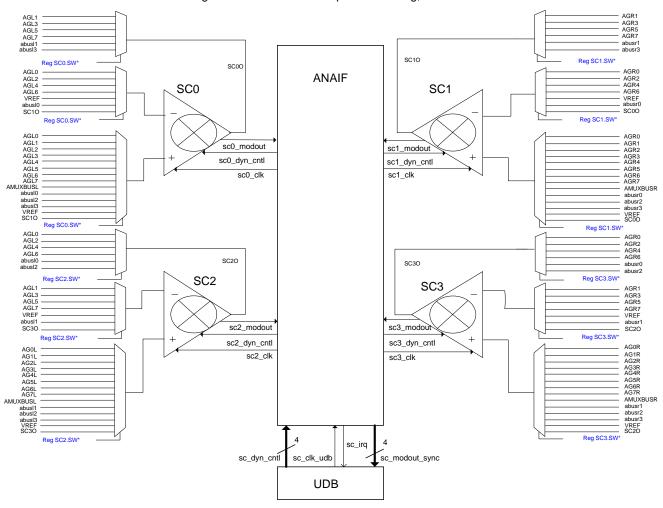

|            | 30. | Switched Capacitor/Continuous Time    | 345 |

|            | 31. | Analog Routing                        | 359 |

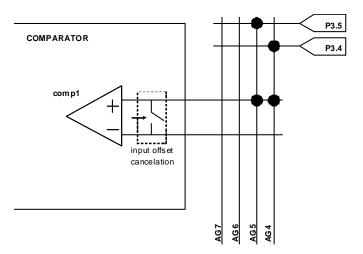

|            | 32. | Comparators                           | 375 |

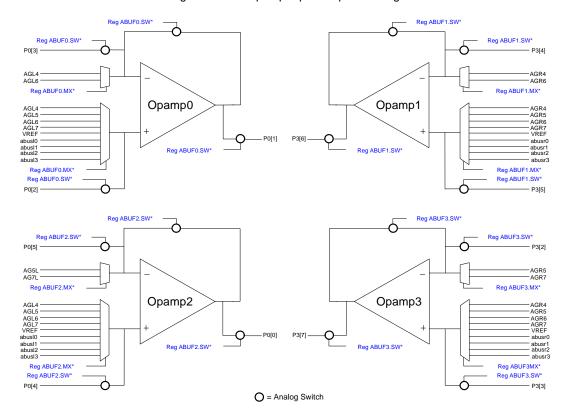

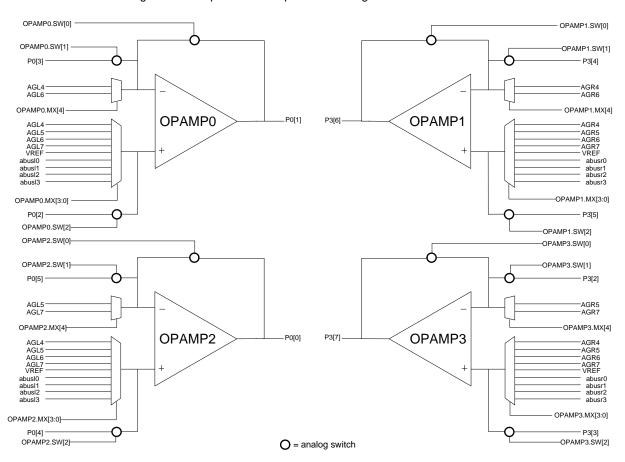

|            | 33. | Opamp                                 | 379 |

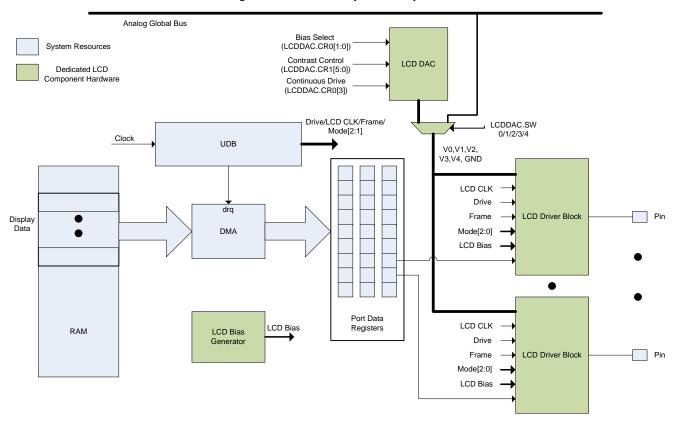

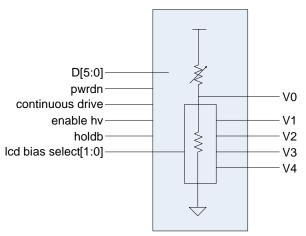

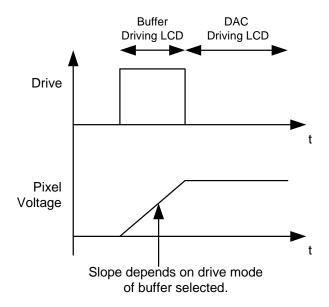

|            | 34. | LCD Direct Drive                      |     |

|            | 35. | CapSense <sup>®</sup>                 | 397 |

|            | 36. | Temperature Sensor                    | 403 |

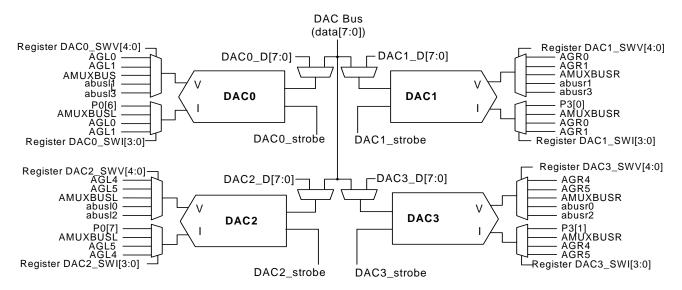

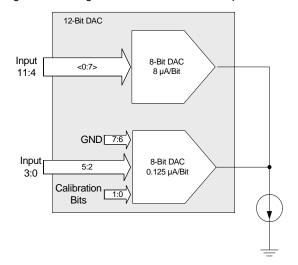

|            | 37. | Digital-to-Analog Converter           | 409 |

|            | 38. | Precision Reference                   | 413 |

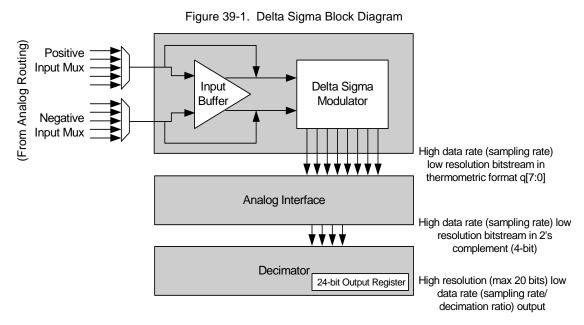

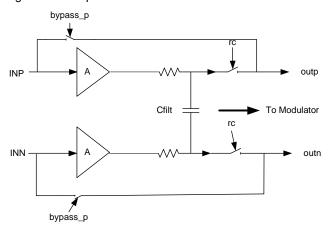

|            | 39. | Delta Sigma Converter                 | 417 |

|            | 40. | Successive Approximation Register ADC | 437 |

| Section G: | Pro | gram and Debug                        | 441 |

|            | 41. | Test Controller                       | 443 |

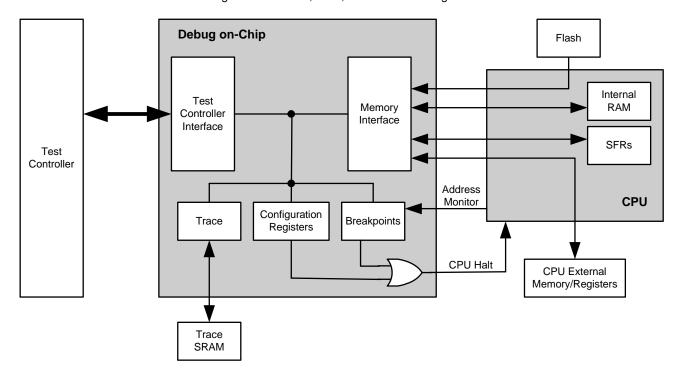

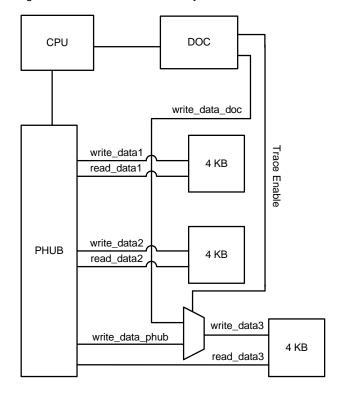

|            | 42. | 8051 Debug on-Chip                    | 455 |

|            | 43. | Cortex-M3 Debug and Trace             | 465 |

|            | 44. | Nonvolatile Memory Programming        | 473 |

| Glossary   |     |                                       | 479 |

| Index      |     |                                       | 495 |

# Contents

| Section | A: Ov | rerview                                      | 21 |

|---------|-------|----------------------------------------------|----|

|         | Docu  | ument Revision History                       | 21 |

| 1.      | Intro | duction                                      | 23 |

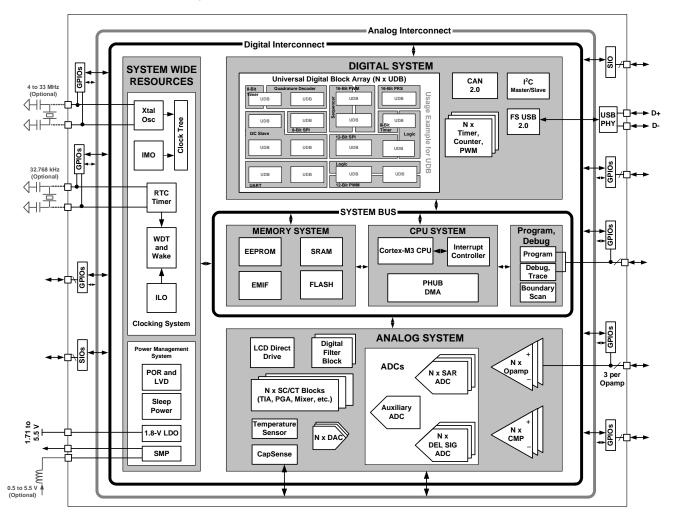

|         | 1.1   | Top Level Architecture                       | 23 |

|         | 1.2   | Features                                     |    |

|         | 1.3   | CPU System                                   | 26 |

|         |       | 1.3.1 Processor                              | 26 |

|         |       | 1.3.2 Interrupt Controller                   | 26 |

|         |       | 1.3.3 DMA Controller                         | 26 |

|         |       | 1.3.4 Cache Controller                       | 26 |

|         | 1.4   | Memory                                       | 26 |

|         | 1.5   | System Wide Resources                        | 27 |

|         |       | 1.5.1 I/O Interfaces                         |    |

|         |       | 1.5.2 Internal Clock Generators              | 27 |

|         |       | 1.5.3 Power Supply                           | 27 |

|         |       | 1.5.3.1 Boost Converter                      |    |

|         |       | 1.5.3.2 Sleep Modes                          |    |

|         | 1.6   | Digital System                               |    |

|         | 1.7   | Analog System                                |    |

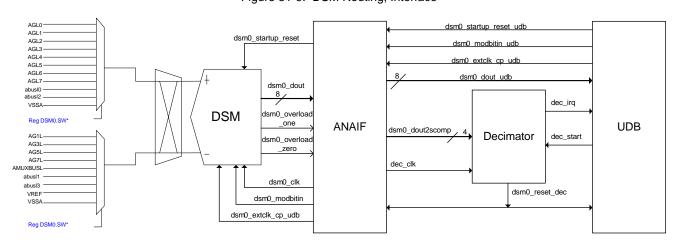

|         |       | 1.7.1 Delta Sigma ADC                        |    |

|         |       | 1.7.2 Successive Approximation Register ADC  |    |

|         |       | 1.7.3 Digital Filter Block                   |    |

|         |       | 1.7.4 Digital-to-Analog Converters           |    |

|         |       | 1.7.5 Additional Analog Subsystem Components |    |

|         | 1.8   | Program and Debug                            | 28 |

| 2.      | Getti | ng Started                                   | 29 |

|         | 2.1   | Support                                      | 29 |

|         | 2.2   | Product Upgrades                             |    |

|         | 2.3   | Development Kits                             |    |

| 3.      | Docu  | ment Construction                            | 31 |

|         | 3.1   | Major Sections                               | 31 |

|         | 3.2   | Documentation Conventions                    |    |

|         |       | 3.2.1 Register Conventions                   | 31 |

|         |       | 3.2.2 Numeric Naming                         |    |

|         |       | 3.2.3 Units of Measure                       | 32 |

|         |       | 3.2.4 Acronyms                               | 32 |

| Section | B: CP | PU System                                    | 35 |

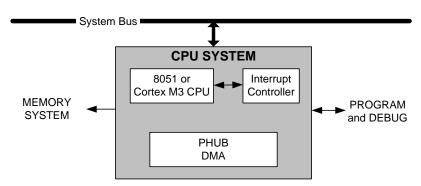

|         | Top   | Level Architecture                           | 35 |

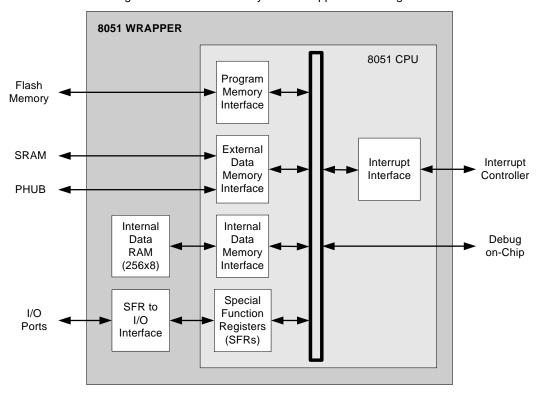

| 4. | 8051  | Core                                                        | 37 |

|----|-------|-------------------------------------------------------------|----|

|    | 4.1   | Features                                                    | 37 |

|    | 4.2   | Block Diagram                                               | 37 |

|    | 4.3   | How It Works                                                |    |

|    |       | 4.3.1 Memory Spaces                                         | 38 |

|    |       | 4.3.2 Instruction Set                                       | 38 |

|    |       | 4.3.3 8051 Core Enhancements                                | 38 |

|    |       | 4.3.4 Interrupt Controller Interface                        | 38 |

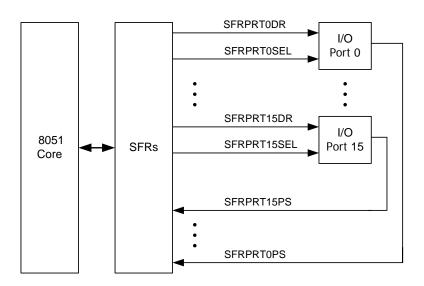

|    | 4.4   | CY 8051 Wrapper                                             |    |

|    |       | 4.4.1 SFR – I/O Interface                                   | 39 |

|    | 4.5   | 8051 Instructions                                           | 39 |

|    |       | 4.5.1 Internal Data Space Map                               | 39 |

|    |       | 4.5.2 Addressing Modes                                      | 39 |

|    |       | 4.5.3 Arithmetic Logic Unit Functions                       | 40 |

|    |       | 4.5.3.1 Arithmetic Instructions                             | 40 |

|    |       | 4.5.3.2 Logical Instructions                                | 41 |

|    |       | 4.5.3.3 Data Transfer Instructions                          | 42 |

|    |       | 4.5.3.4 Boolean Instructions1                               | 43 |

|    |       | 4.5.3.5 Program Branching Instructions                      | 43 |

|    |       | 4.5.3.6 Instruction Set Details                             | 44 |

|    | 4.6   | 8051 Special Function Registers (SFRs)                      | 62 |

|    |       | 4.6.1 SFRs                                                  | 62 |

|    |       | 4.6.2 Dual Data Pointer SFRs                                | 63 |

|    |       | 4.6.3 24-Bit Data Pointer SFRs                              | 64 |

|    |       | 4.6.4 I/O Port Access SFRs                                  | 65 |

|    |       | 4.6.5 Interrupt Enable (IE)                                 | 65 |

|    | 4.7   | Program and External Data Spaces                            | 66 |

|    |       | 4.7.1 Program Space                                         | 66 |

|    |       | 4.7.2 External Data Space                                   | 66 |

|    | 4.8   | CPU Halt Mechanisms                                         | 66 |

| 5. | Corte | x™-M3 Microcontroller                                       | 67 |

|    | 5.1   | Features                                                    | 67 |

|    | 5.2   | How it Works                                                |    |

|    | 0.2   | 5.2.1 Registers                                             |    |

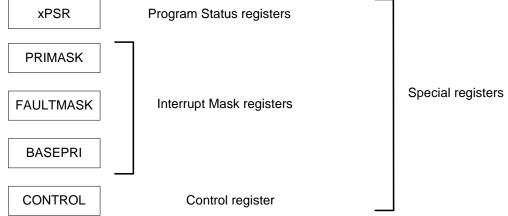

|    |       | 5.2.1.1 Special Registers                                   |    |

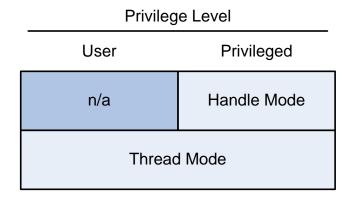

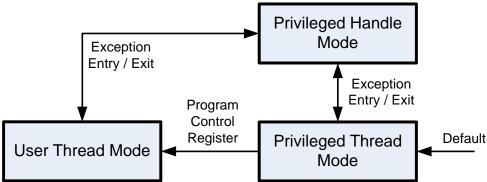

|    |       | 5.2.2 Operating Modes                                       |    |

|    |       | 5.2.3 Pipelining                                            | 70 |

|    |       | 5.2.4 Thumb-2 Instruction Set                               |    |

|    |       | 5.2.4.1 Data Processing Operations                          |    |

|    |       | 5.2.4.2 Load Store Operations                               |    |

|    |       | 5.2.4.3 Branch Operations                                   |    |

|    |       | 5.2.4.4 Instruction Barrier and Memory Barrier Instructions |    |

|    |       | 5.2.4.5 Saturation Operations                               |    |

|    |       | 5.2.5 SysTick Timer                                         |    |

|    |       | 5.2.6 Debug and Trace:                                      |    |

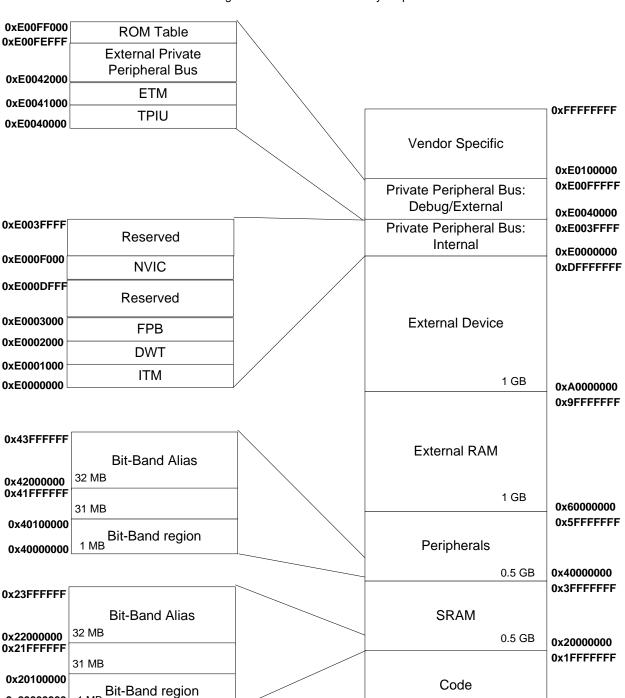

|    | 5.3   | Memory Map                                                  |    |

|    | 2.0   | 5.3.1 Bus Interface to SRAM Memory                          |    |

|    | 5.4   | Exceptions                                                  |    |

|    | J     | 5.4.1 Priority Definitions                                  |    |

|    |       | 5.4.2 Fault Exceptions                                      |    |

|    |       | 5.4.3 System Call Exceptions                                |    |

|    | 5.5   | Nested Vector Interrupt Controller (NVIC)                   |    |

|    | -     | 1 /                                                         | _  |

|    |            | 5.5.1 Basic Interrupt Configuration                   | 79 |  |  |  |

|----|------------|-------------------------------------------------------|----|--|--|--|

|    |            | 5.5.1.1 Example Procedures in Setting Up an Interrupt | 79 |  |  |  |

|    |            | 5.5.2 Nested Interrupts                               | 79 |  |  |  |

|    |            | 5.5.3 Tail-Chaining Interrupts                        | 79 |  |  |  |

|    |            | 5.5.4 Late Arrivals                                   | 79 |  |  |  |

|    |            | 5.5.5 Interrupt Latency                               | 80 |  |  |  |

|    |            | 5.5.6 Faults Related to Interrupts                    | 80 |  |  |  |

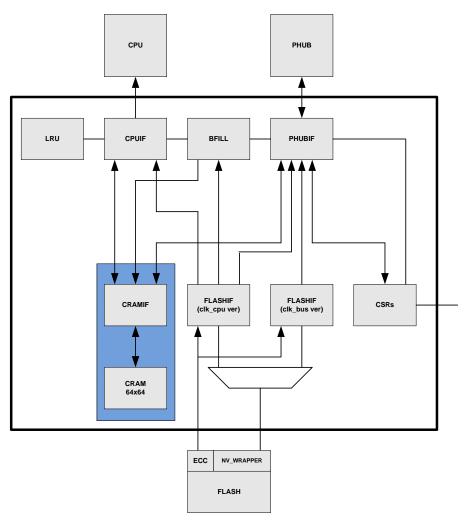

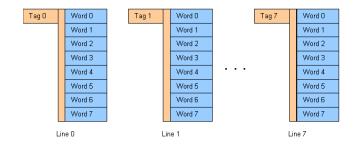

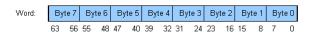

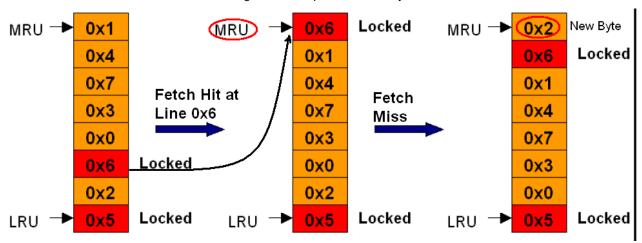

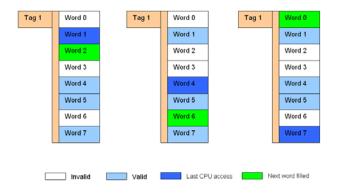

| 6. | PSoC       | 3 Cache Controller                                    | 81 |  |  |  |

| ٥. |            |                                                       |    |  |  |  |

|    | 6.1        | Features                                              |    |  |  |  |

|    | 6.2        | Block Diagram                                         |    |  |  |  |

|    | 6.3        | Cache Memory Organization and Addressing              |    |  |  |  |

|    |            | 6.3.1 Cache Operation                                 |    |  |  |  |

|    |            |                                                       |    |  |  |  |

|    |            | 5                                                     |    |  |  |  |

|    |            | ·                                                     |    |  |  |  |

|    |            | 6.3.5 Background Fill (BFILL):                        |    |  |  |  |

|    |            | 6.3.6.1 Interrupts                                    |    |  |  |  |

|    |            | 6.3.7 Flash Low Power Mode                            |    |  |  |  |

|    |            | 0.5.7 Flasii Low Powei Mode                           | 00 |  |  |  |

| 7. | PSoC       | 5 Cache Controller                                    | 87 |  |  |  |

|    | 7.1        | Features                                              | 87 |  |  |  |

|    | 7.2        | Block Diagram                                         |    |  |  |  |

|    | 7.3        | Cache Enabling and Disabling                          | 88 |  |  |  |

|    | 7.4        | Code Protection and Security                          |    |  |  |  |

|    | 7.5        | Invalidating the Cache Line                           |    |  |  |  |

|    | 7.6<br>7.7 | 7.5.1 Measuring Cache Hits or Misses                  |    |  |  |  |

|    |            | Cache Induced Flash Low Power Mode                    |    |  |  |  |

|    |            | Sleep Mode Behavior                                   |    |  |  |  |

|    | 7.8        | Cache Limitations                                     | 88 |  |  |  |

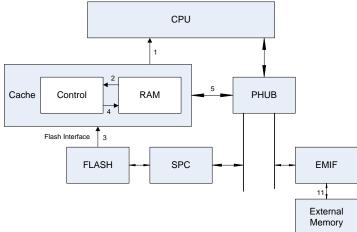

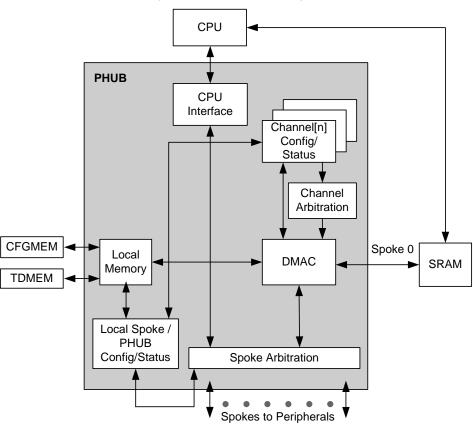

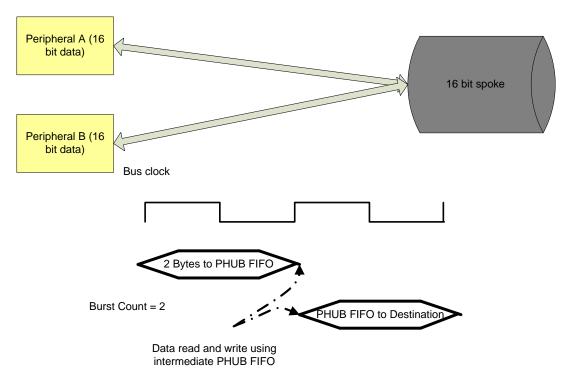

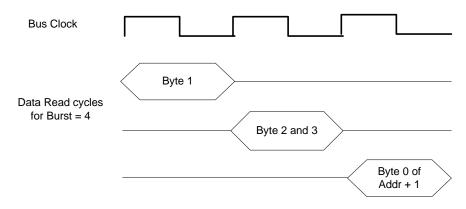

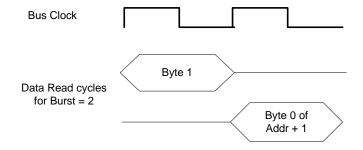

| 8. | PHUR       | B and DMAC                                            | 91 |  |  |  |

| ٥. |            |                                                       | _  |  |  |  |

|    | 8.1        | PHUB                                                  |    |  |  |  |

|    |            | 8.1.1 Features                                        |    |  |  |  |

|    |            | 8.1.2 Block Diagram                                   |    |  |  |  |

|    |            | 8.1.4 Arbiter                                         |    |  |  |  |

|    | 8.2        | DMA Controller                                        |    |  |  |  |

|    | 0.2        | 8.2.1 Local Memory                                    |    |  |  |  |

|    |            | 8.2.2 How the DMAC Works                              |    |  |  |  |

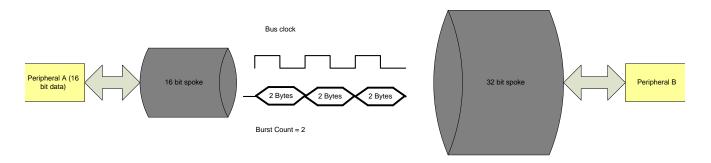

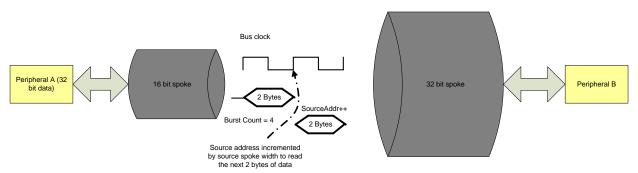

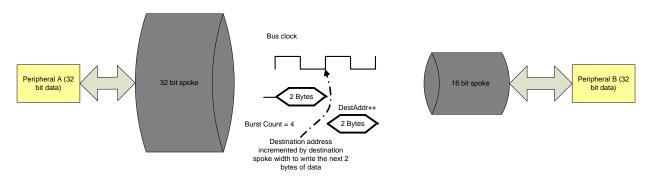

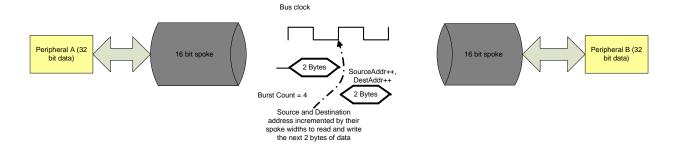

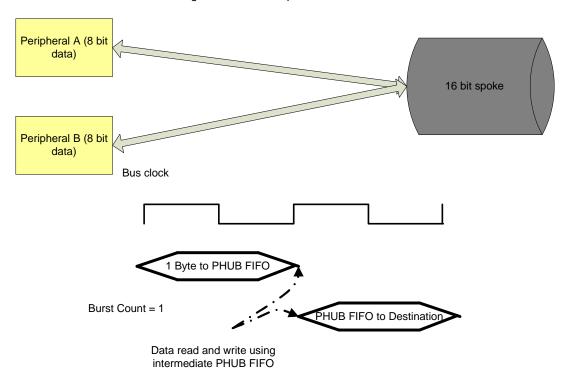

|    |            | 8.2.2.1 Interspoke Transfers                          |    |  |  |  |

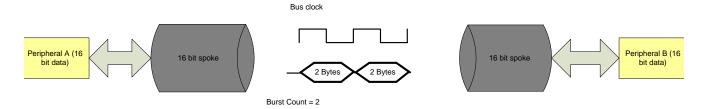

|    |            | 8.2.2.2 Intraspoke Transfer                           |    |  |  |  |

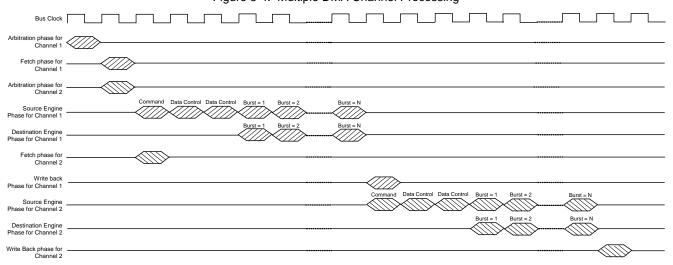

|    |            | 8.2.2.3 Handling Multiple DMA Channels                |    |  |  |  |

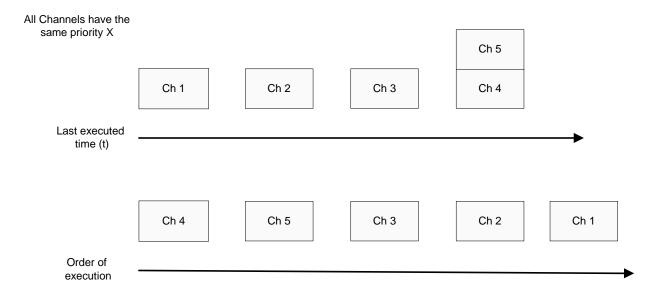

|    |            | 8.2.2.4 DMA Channel Priority                          |    |  |  |  |

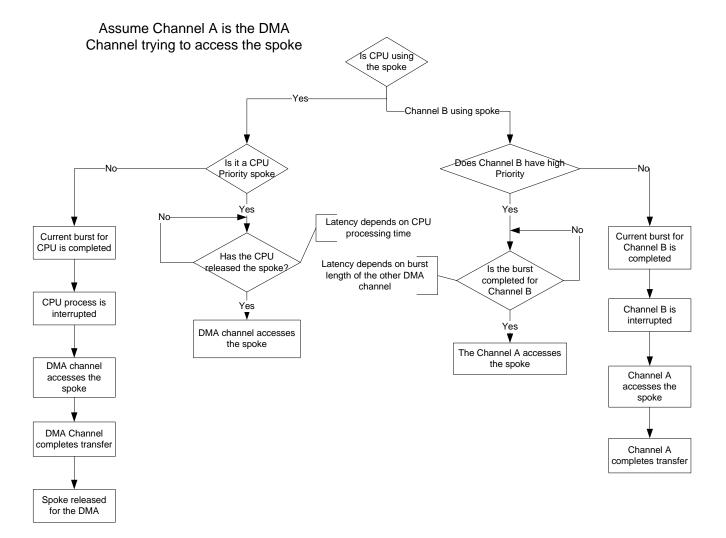

|    |            | 8.2.2.5 DMA Latency in case of Nonideal Conditions    |    |  |  |  |

|    |            | 8.2.2.6 Request per Burst Bit                         |    |  |  |  |

|    |            | 8.2.2.7 Work Sep Bit                                  |    |  |  |  |

|    | 8.3        | DMA Transaction Modes                                 |    |  |  |  |

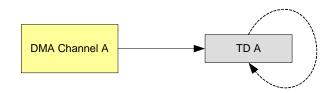

|    |            | 8.3.1 Simple DMA                                      |    |  |  |  |

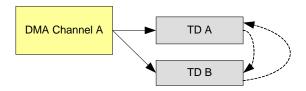

|    |            | 8.3.2 Auto Repeat DMA                                 |    |  |  |  |

|    |            | 8.3.3 Ping Pong DMA                                   |    |  |  |  |

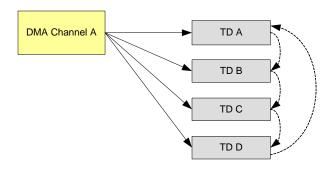

|    |            | 8.3.4 Circular DMA                                    |    |  |  |  |

|    |            |                                                       |    |  |  |  |

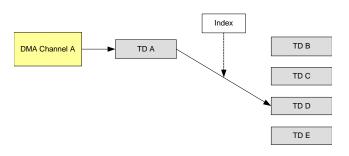

|         |                                                           | 8.3.5 7.3.5 Indexed DMA                                                             |                          |

|---------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------|

|         |                                                           | 8.3.6 Scatter Gather DMA                                                            | 105                      |

|         |                                                           | 8.3.7 Packet Queuing DMA                                                            |                          |

|         |                                                           | 8.3.8 Nested DMA                                                                    |                          |

|         | 8.4                                                       | Register List                                                                       | 106                      |

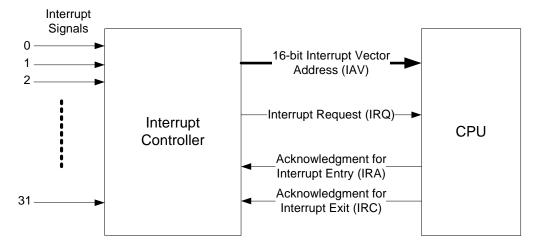

| 9.      | Interr                                                    | upt Controller                                                                      | 107                      |

|         | 9.1                                                       | Features                                                                            |                          |

|         | 9.2                                                       | Block Diagram                                                                       |                          |

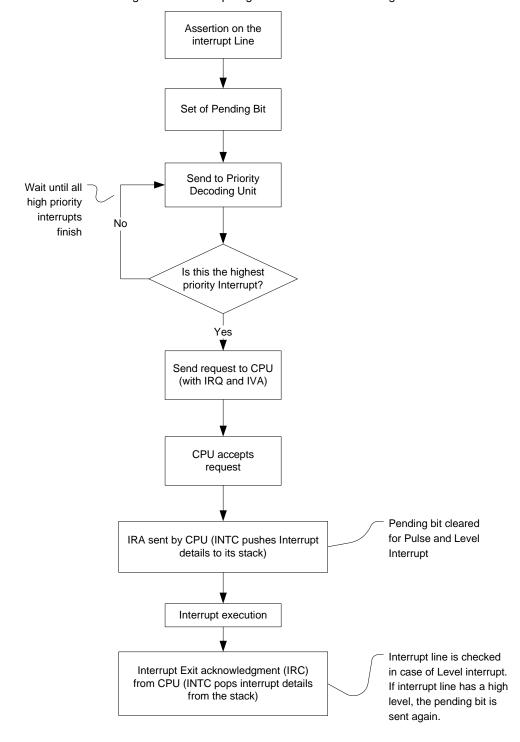

|         | 9.3                                                       | How It Works                                                                        |                          |

|         |                                                           | 9.3.1 Enabling Interrupts                                                           |                          |

|         |                                                           | 9.3.2 Pending Interrupts                                                            |                          |

|         |                                                           | 9.3.3 Interrupt Priority                                                            |                          |

|         |                                                           | 9.3.4 Level versus Pulse Interrupt                                                  |                          |

|         | 9.4                                                       | 9.3.5 Interrupt Execution                                                           |                          |

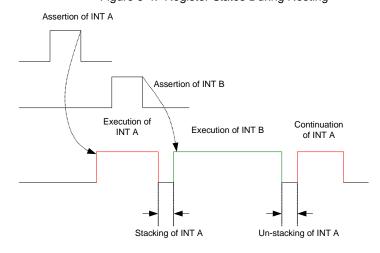

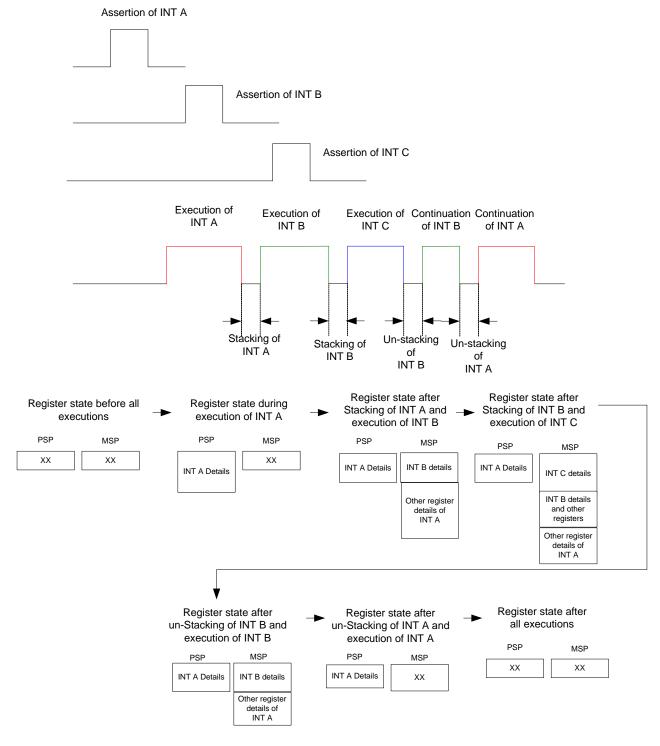

|         | 9.4                                                       | 9.4.1 Active Interrupts                                                             |                          |

|         |                                                           | 9.4.2 Interrupt Nesting                                                             |                          |

|         |                                                           | 9.4.3 Interrupt Vector Addresses                                                    |                          |

|         |                                                           | 9.4.4 Sleep Mode Behavior                                                           |                          |

|         | 9.5                                                       | PSoC 5 Features                                                                     |                          |

|         | 0.0                                                       | 9.5.1 Active Interrupts                                                             |                          |

|         |                                                           | 9.5.2 Interrupt Nesting                                                             |                          |

|         |                                                           | 9.5.3 Interrupt Vector Addresses                                                    |                          |

|         |                                                           | 9.5.4 Tail Chaining                                                                 |                          |

|         |                                                           | 9.5.5 Late Arrival Interrupts                                                       | 116                      |

|         |                                                           | 9.5.6 Exceptions                                                                    | 117                      |

|         |                                                           | 9.5.7 Interrupt Masking                                                             | 117                      |

|         | 9.6                                                       | Interrupt Controller and Power Modes                                                | 117                      |

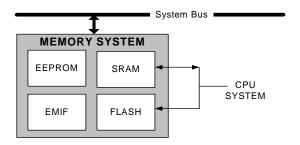

| Section | C: Me                                                     | mory                                                                                | 119                      |

|         | Top l                                                     | Level Architecture                                                                  | 119                      |

| 10      | . Nonv                                                    | olatile Latch                                                                       | 121                      |

|         | 10.1                                                      | Features                                                                            |                          |

|         | 10.1                                                      | 1 Galuigs                                                                           | 1 71                     |

|         | 10.2                                                      |                                                                                     |                          |

|         |                                                           | Device Configuration NV Latch                                                       | 121                      |

|         |                                                           | Device Configuration NV Latch                                                       | 121<br>121               |

|         |                                                           | Device Configuration NV Latch                                                       | 121<br>121<br>122        |

|         |                                                           | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]  10.2.2 XRESMEN  10.2.3 CFGSPEED | 121<br>121<br>122<br>122 |

|         |                                                           | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]  10.2.2 XRESMEN  10.2.3 CFGSPEED | 121<br>121<br>122<br>122 |

|         |                                                           | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.3                                                      | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.4                                                      | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.4                                                      | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

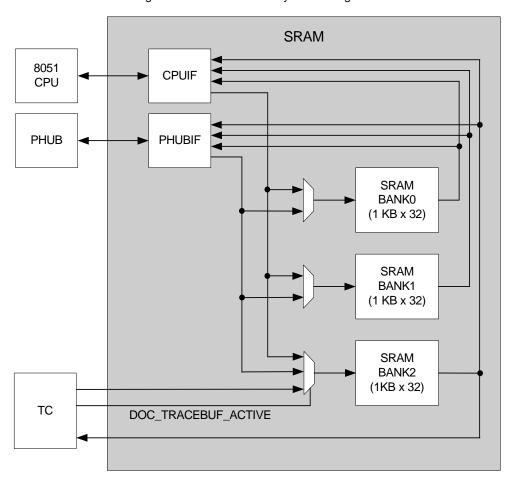

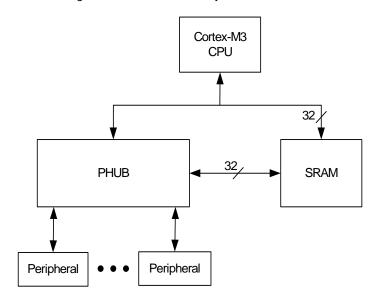

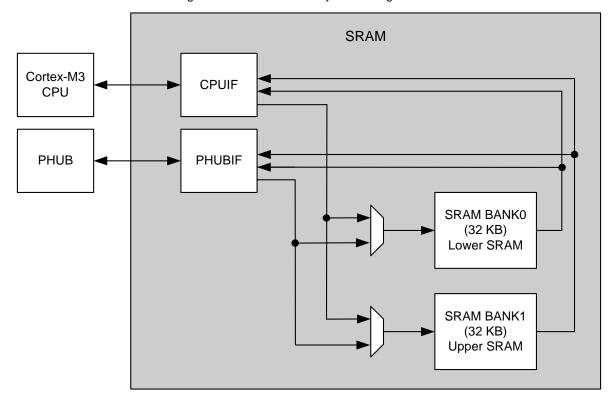

| 11.     | 10.4                                                      | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

| 11.     | 10.4<br>10.5                                              | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

| 11.     | 10.4<br>10.5<br>. SRAM                                    | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

| 11.     | 10.4<br>10.5<br>• SRAN                                    | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.4<br>10.5<br>• SRAN<br>11.1<br>11.2<br>11.3            | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.4<br>10.5<br>• SRAN<br>11.1<br>11.2<br>11.3            | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         | 10.4<br>10.5<br>• SRAN<br>11.1<br>11.2<br>11.3<br>• Flash | Device Configuration NV Latch  10.2.1 PRTxRDM[1:0]                                  |                          |

|         |        | How It Works                              |     |

|---------|--------|-------------------------------------------|-----|

|         | 12.4   | ECC Error Detection and Interrupts        | 130 |

| 13.     | EEPR   | OM                                        | 131 |

|         | 13.1   | Features                                  | 131 |

|         | 13.2   | Block Diagram                             | 131 |

|         | 13.3   | How It Works                              | 132 |

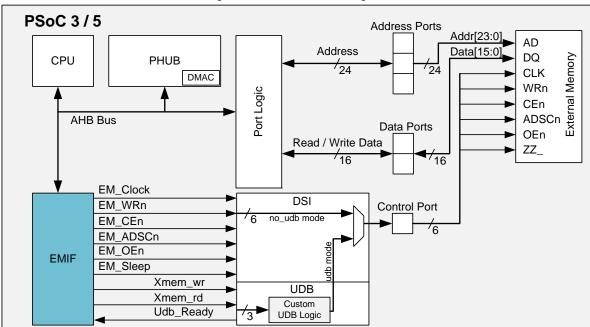

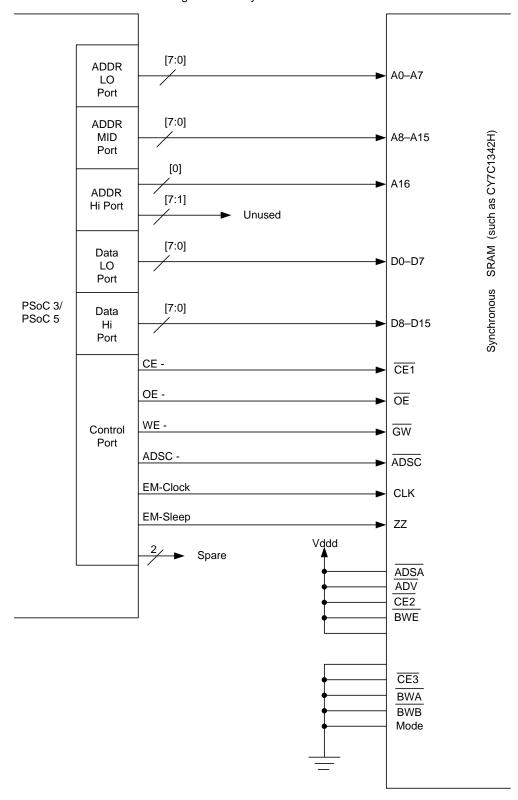

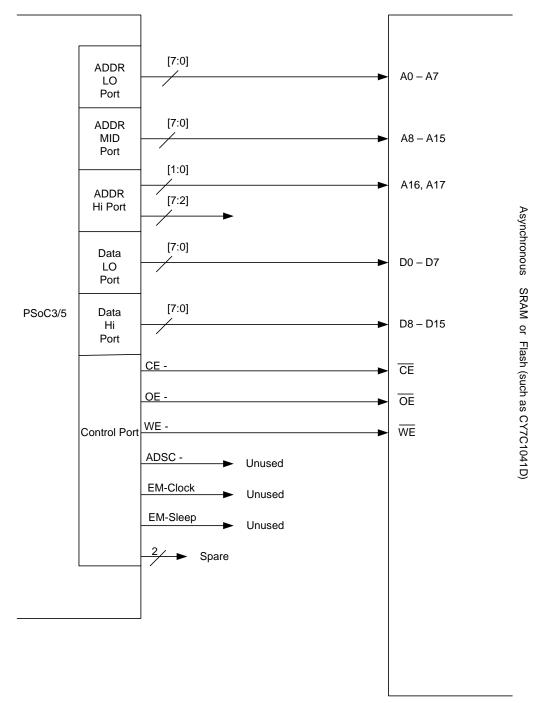

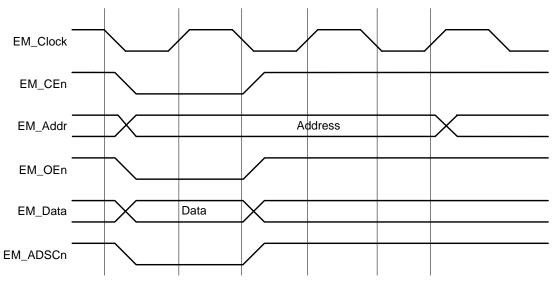

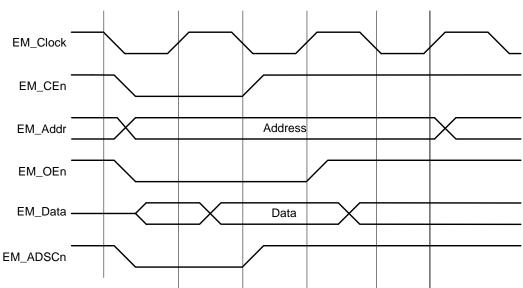

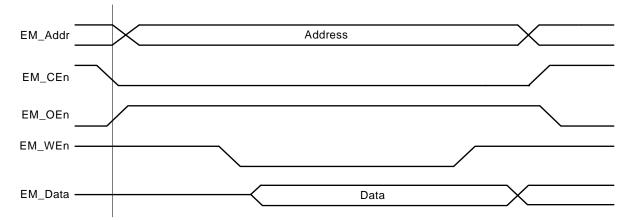

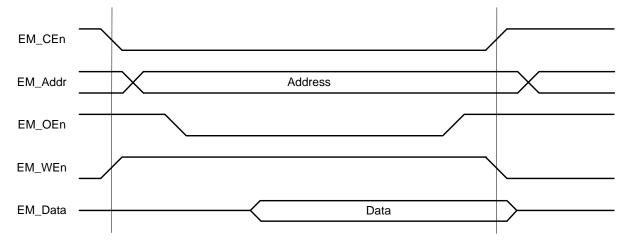

| 14.     | EMIF   |                                           | 133 |

|         | 14.1   | Features                                  | 133 |

|         | 14.2   | Block Diagram                             |     |

|         | 14.3   | How It Works                              |     |

|         |        | 14.3.1 List of EMIF Registers             |     |

|         |        | 14.3.2 External Memory Support            |     |

|         |        | 14.3.3 Sleep Mode Behavior                | 137 |

|         | 14.4   | EMIF Timing                               | 138 |

|         | 14.5   | Using EMIF with Memory-Mapped Peripherals | 140 |

|         | 14.6   | Additional Configuration Guidelines       | 140 |

|         |        | 14.6.1 Address Bus Configuration          | 140 |

|         |        | 14.6.2 Data Bus Configuration             | 140 |

|         |        | 14.6.3 16-bit Memory Transfers            | 140 |

|         |        | 14.6.4 8-bit Memory Transfers             | 140 |

| 15.     | Memo   | ory Map                                   | 141 |

|         | 15.1   | Features                                  | 141 |

|         | 15.2   | Block Diagram                             | 141 |

|         | 15.3   | How It Works                              | 141 |

|         |        | 15.3.1 PSoC 3 Memory Map                  | 142 |

|         |        | 15.3.2 PSoC 5 Memory Map                  | 143 |

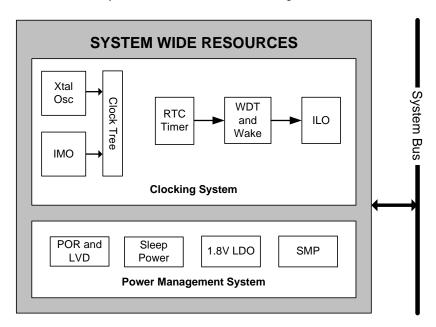

| Section | D: Sys | stem Wide Resources                       | 145 |

|         | Top I  | _evel Architecture                        | 145 |

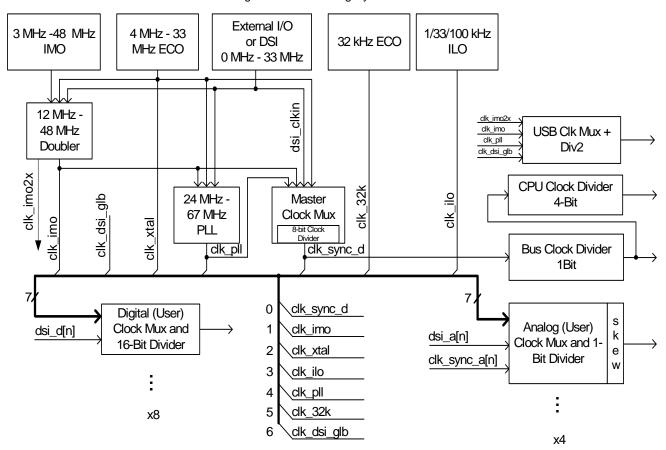

| 16.     | Clock  | king System                               | 147 |

|         | 16.1   | Features                                  | 147 |

|         | 16.2   | Block Diagram                             |     |

|         | 16.3   | Clock Sources                             |     |

|         |        | 16.3.1 Internal Oscillators               | 148 |

|         |        | 16.3.1.1 Internal Main Oscillator         | 149 |

|         |        | 16.3.1.2 Internal Low Speed Oscillator    | 149 |

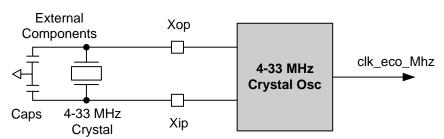

|         |        | 16.3.2 External Oscillators               |     |

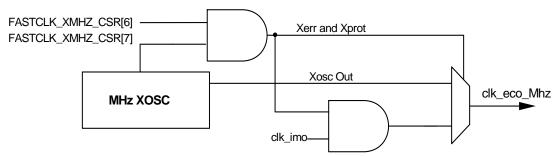

|         |        | 16.3.2.1 MHz Crystal Oscillator           | 150 |

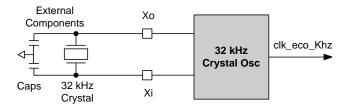

|         |        | 16.3.2.2 32.768 kHz Crystal Oscillator    | 151 |

|         |        | 16.3.3 Oscillator Summary                 | 152 |

|         |        | 16.3.4 DSI Clocks                         | 152 |

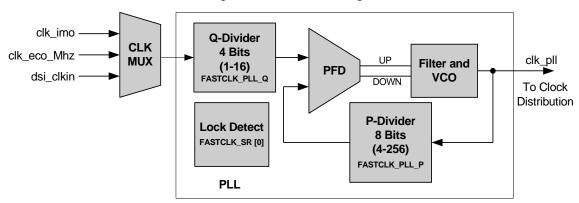

|         |        | 16.3.5 Phase-Locked Loop                  |     |

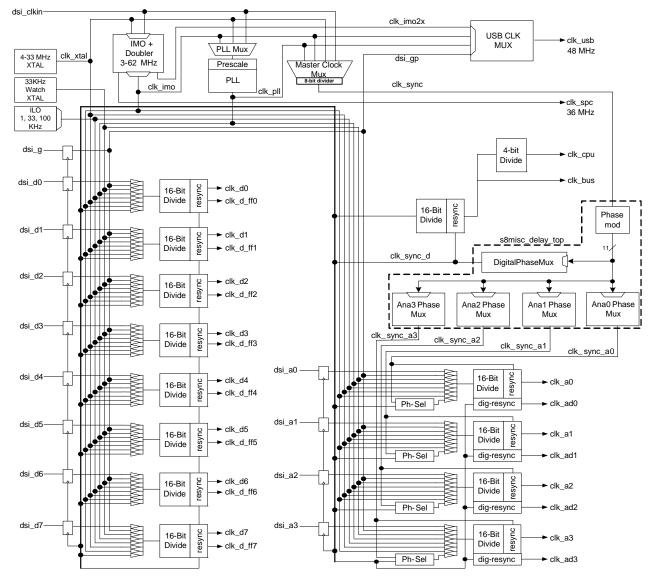

|         | 16.4   | Clock Distribution                        |     |

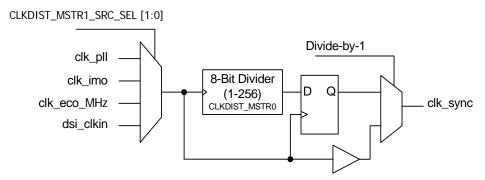

|         |        | 16.4.1 Master Clock Mux                   | 155 |

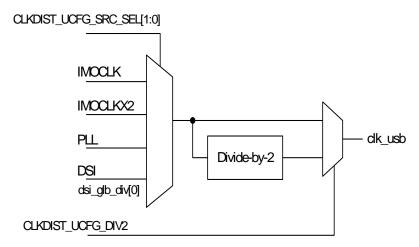

|         |        | 16.4.2 USB Clock                          |     |

|         |        | 16.4.3 Clock Dividers                     |     |

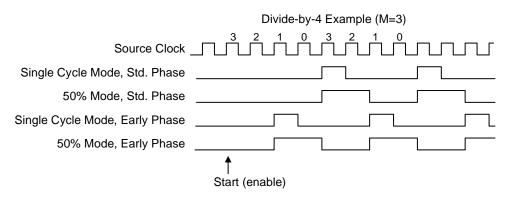

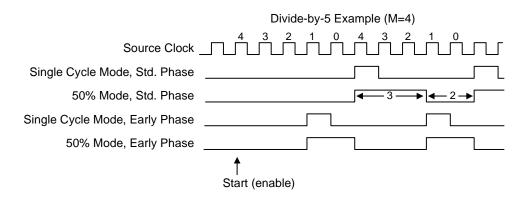

|         |        | 16.4.3.1 Single Cycle Pulse Mode          |     |

|         |        | 16.4.3.2 50% Duty Cycle Mode              |     |

|         |        | 16.4.3.3 Early Phase Option               |     |

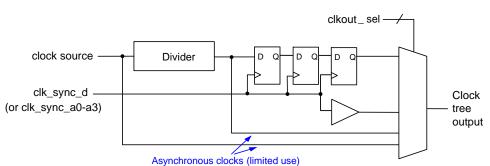

|         |        | 16.4.4 Clock Synchronization              | 158 |

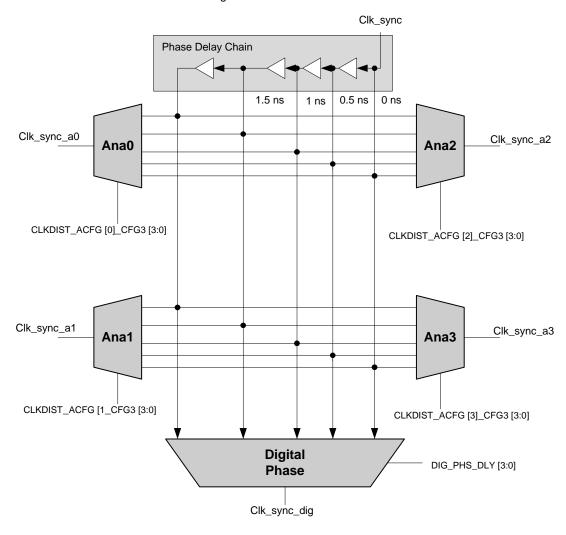

|     |       | 16.4.5 Phase Selection and Control                      |     |

|-----|-------|---------------------------------------------------------|-----|

|     |       | 16.4.6 Divider Update                                   |     |

|     |       | 16.4.7 Power Gating of Clock Outputs                    |     |

|     |       | 16.4.8 System Clock                                     | 160 |

|     |       | 16.4.9 Asynchronous Clocks                              | 160 |

|     | 16.5  | Low Power Mode Operation                                | 160 |

|     | 16.6  | Clock Naming Summary                                    | 161 |

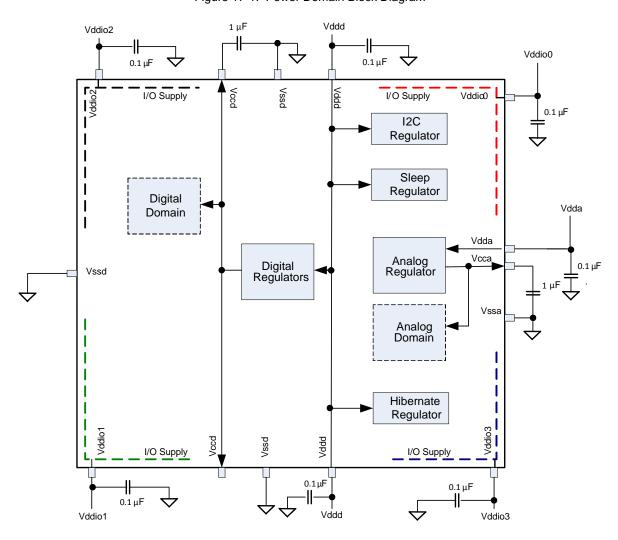

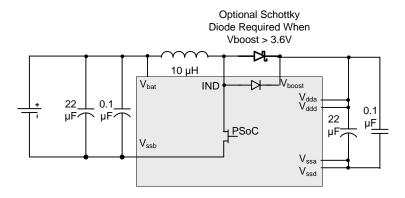

| 17. | Powe  | r Supply and Monitoring                                 | 163 |

|     | 17.1  | Features                                                | 163 |

|     | 17.2  | Block Diagram                                           | 164 |

|     | 17.3  | How It Works                                            | 165 |

|     |       | 17.3.1 Regulator Summary                                | 165 |

|     |       | 17.3.1.1 Internal Regulators                            |     |

|     |       | 17.3.1.2 Sleep Regulator                                |     |

|     |       | 17.3.1.3 Hibernate Regulator                            |     |

|     |       | 17.3.2 Boost Converter                                  |     |

|     |       | 17.3.2.1 Modes of Operation                             |     |

|     |       | 17.3.2.2 Status Monitoring                              |     |

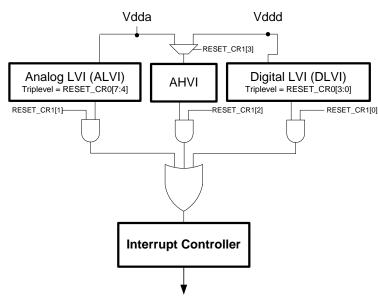

|     |       | 17.3.3 Voltage Monitoring                               |     |

|     |       | 17.3.3.1 Low Voltage Interrupt                          |     |

|     |       | 17.3.3.2 High Voltage Interrupt                         |     |

|     |       | 17.3.3.3 Processing a Low/High Voltage Detect Interrupt |     |

|     | 47.4  | 17.3.3.4 Reset on a Voltage Monitoring Interrupt        |     |

|     | 17.4  | Register Summary                                        | 168 |

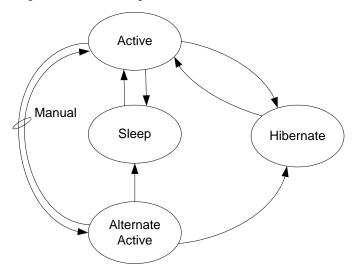

| 18. | Low F | Power Modes                                             | 169 |

|     | 18.1  | Features                                                | 169 |

|     | 18.2  | Active Mode                                             |     |

|     |       | 18.2.1 Entering Active Mode                             |     |

|     |       | 18.2.2 Exiting Active Mode                              | 171 |

|     | 18.3  | Alternative Active Mode                                 |     |

|     |       | 18.3.1 Entering Alternative Active Mode                 |     |

|     |       | 18.3.2 Exiting Alternative Active Mode                  |     |

|     | 18.4  | Sleep Mode                                              |     |

|     |       | 18.4.1 Entering Sleep Mode                              |     |

|     |       | 18.4.2 Exiting Sleep Mode                               |     |

|     | 18.5  | Hibernate Mode                                          |     |

|     |       | 18.5.1 Entering Hibernate Mode                          |     |

|     | 400   | 18.5.2 Exiting Hibernate Mode                           |     |

|     | 18.6  | Timewheel                                               |     |

|     |       | 18.6.1 Central Timewheel (CTW)                          |     |

|     | 40.7  | 18.6.2 Fast Timewheel (FTW)                             |     |

|     | 18.7  | Register List                                           | 1/3 |

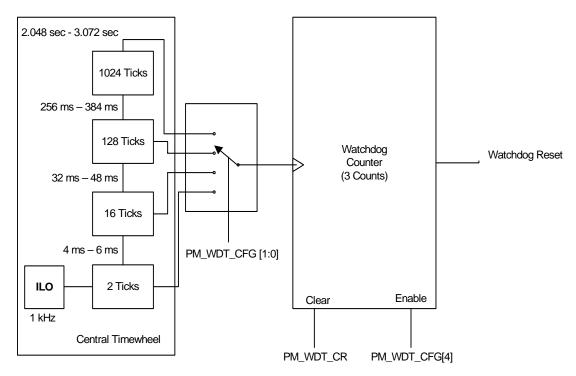

| 19. | Watch | ndog Timer                                              | 175 |

|     | 19.1  | Features                                                |     |

|     | 19.2  | Block Diagram                                           |     |

|     | 19.3  | How It Works                                            |     |

|     |       | 19.3.1 Enabling and Disabling the WDT                   | 176 |

|     |       | 19.3.2 Setting the WDT Time Period and Clearing the WDT |     |

|     |       | 19.3.3 Operation in Low Power Modes                     |     |

|     |       | 19.3.4 Watchdog Protection Settings                     | 176 |

|     | 19.4   | Register List    |                                          | 177 |

|-----|--------|------------------|------------------------------------------|-----|

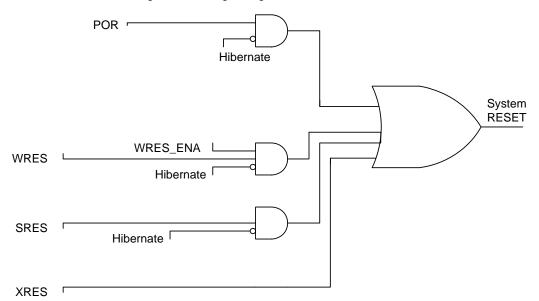

| 20. | Reset  |                  |                                          | 179 |

|     | 20.1   | Reset Sources    |                                          | 179 |

|     |        |                  | on Reset                                 |     |

|     |        |                  | log Reset                                |     |

|     |        |                  | re Initiated Reset                       |     |

|     |        |                  | al Reset                                 |     |

|     |        | 20.1.5 Identify  | ring Reset Sources                       | 180 |

|     | 20.2   | Reset Diagram    |                                          | 180 |

|     | 20.3   | Reset Summary    |                                          | 181 |

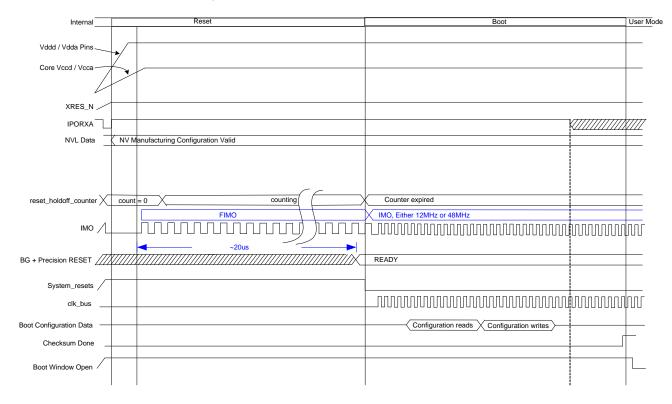

|     | 20.4   | Boot Process and | Timing                                   | 182 |

|     |        | 20.4.1 Manufa    | acturing Configuration NV Latch          | 183 |

|     |        | 20.4.1.1         | Device Configuration NV Latch            |     |

|     |        |                  | hase                                     |     |

|     |        |                  | ode                                      |     |

|     | 20.5   | Register List    |                                          | 185 |

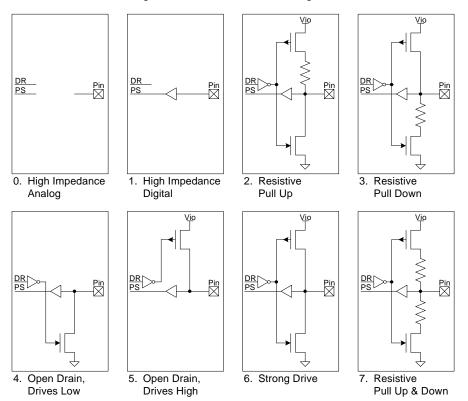

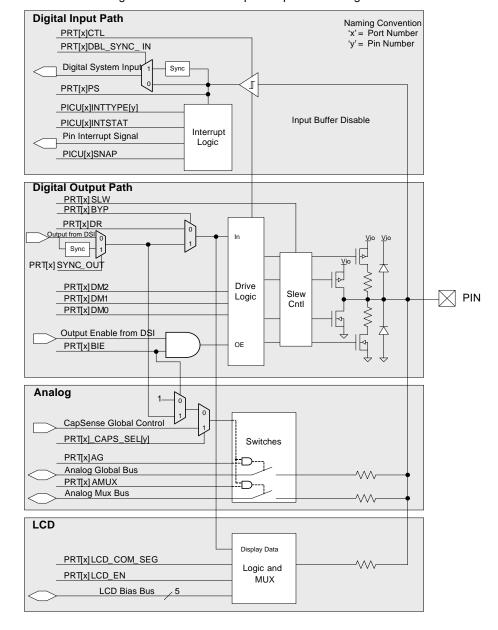

| 21. | I/O Sy | stem             |                                          | 187 |

|     | 21.1   | Features         |                                          | 187 |

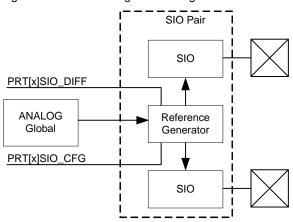

|     | 21.2   | Block Diagrams   |                                          | 188 |

|     | 21.3   | How It Works     |                                          | 190 |

|     |        | 21.3.1 Usage     | Modes and Configuration                  | 190 |

|     |        | 21.3.2 I/O Driv  | /e Modes                                 | 191 |

|     |        | 21.3.2.1         | Drive Mode on Reset                      |     |

|     |        | 21.3.2.2         | High Impedance Analog                    |     |

|     |        | 21.3.2.3         | High Impedance Digital                   |     |

|     |        | 21.3.2.4         | Resistive Pull Up or Resistive Pull Down |     |

|     |        | 21.3.2.5         | Open Drain, Drives High and Drives Low   |     |

|     |        | 21.3.2.6         | Strong Drive                             |     |

|     |        | 21.3.2.7         | Resistive Pull Up and Pull Down          |     |

|     |        |                  | ate Control                              |     |

|     |        | -                | I/O Controlled by Port Register          |     |

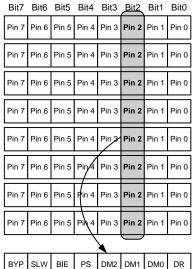

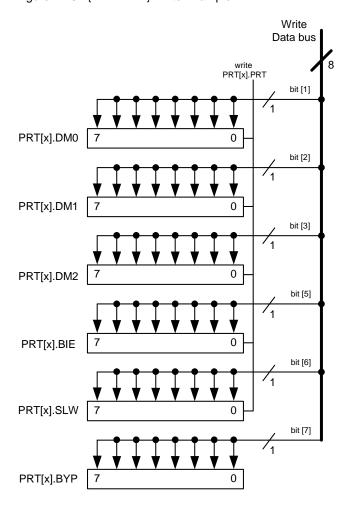

|     |        | 21.3.4.1         | Port Configuration Registers             |     |

|     |        | 21.3.4.2         | Pin Wise Configuration Register Alias    |     |

|     |        | 21.3.4.3         | Port Wide Configuration Register Alias   |     |

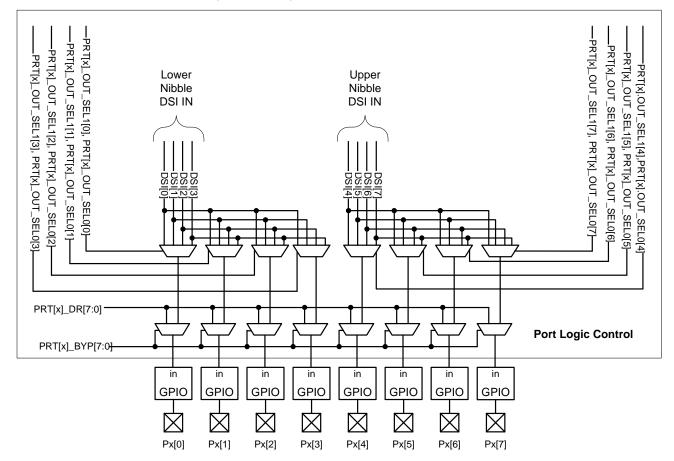

|     |        |                  | GPIO                                     |     |

|     |        |                  | I/O Controlled Through DSI               |     |

|     |        | 21.3.6.1         | DSI Output                               |     |

|     |        | 21.3.6.2         | DSI Input                                |     |

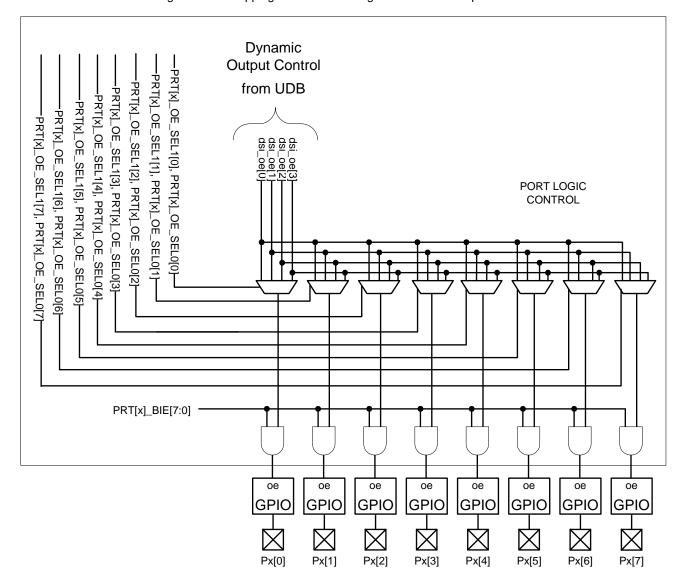

|     |        | 21.3.6.3         | DSI for Output Enable Control            |     |

|     |        |                  | rive                                     |     |

|     |        |                  | nse                                      |     |

|     |        |                  | al Memory Interface (EMIF)               |     |

|     |        |                  | nctions and Features                     |     |

|     |        | 21.3.11          | Regulated Output Level                   |     |

|     |        | 21.3.11.2        | Adjustable Input Level                   |     |

|     |        | 21.3.11.3        | Hot Swap                                 |     |

|     |        |                  | Functionality                            |     |

|     |        | -                | t Reconfiguration                        |     |

|     |        |                  | Up I/O Configuration                     |     |

|     |        |                  | Itage Tolerance                          |     |

|         |        | 21.3.16 I/O Pov      | ver Supply                                              | 200             |

|---------|--------|----------------------|---------------------------------------------------------|-----------------|

|         |        | 21.3.17 Sleep I      | Mode Behavior                                           | 200             |

|         |        | •                    | ower Behavior                                           |                 |

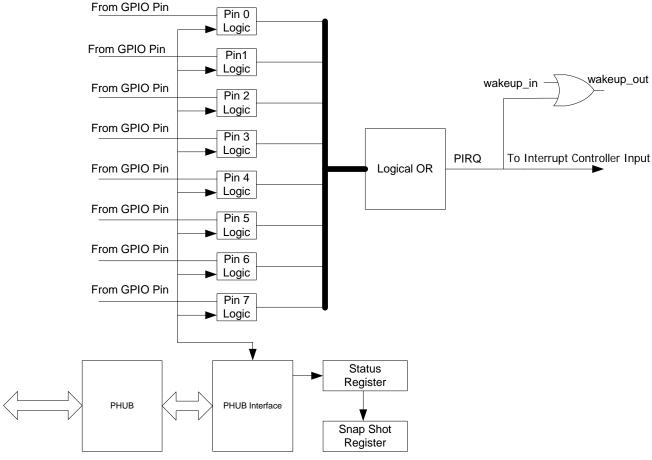

|         | 21.4   | Port Interrupt Con   | troller Unit                                            | 201             |

|         |        | 21.4.1 Feature       | es                                                      | 201             |

|         |        | 21.4.2 Interrup      | ot Controller Block Diagram                             | 201             |

|         |        | 21.4.3 Function      | n and Configuration                                     | 202             |

|         | 21.5   | Register Summar      | y                                                       | 202             |

| 22.     | Flash  | , Configuration      | Protection                                              | 205             |

|         | 22.1   |                      |                                                         |                 |

|         | 22.2   | -                    |                                                         |                 |

|         | 22.3   | •                    | ment Protection                                         |                 |

|         |        |                      | g/Unlocking Segment Configuration Register              |                 |

|         |        |                      | g and Protecting Segments                               |                 |

|         |        |                      | le                                                      |                 |

|         | 22.4   | Frequently Asked 209 | Questions About Best Practices for Flash Protection and | Device Security |

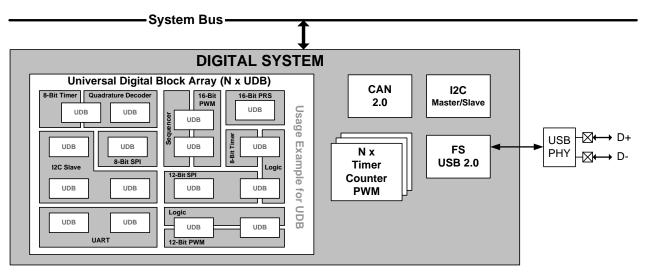

| Section | E: Dig | ital System          |                                                         | 211             |

|         | Top L  | evel Architecture .  |                                                         | 212             |

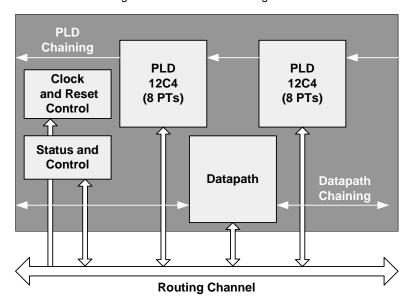

| 23.     | _      | rsal Digital Blo     |                                                         | 213             |

|         | 23.1   | Features             |                                                         | 213             |

|         | 23.2   |                      |                                                         |                 |

|         | 23.3   | •                    |                                                         |                 |

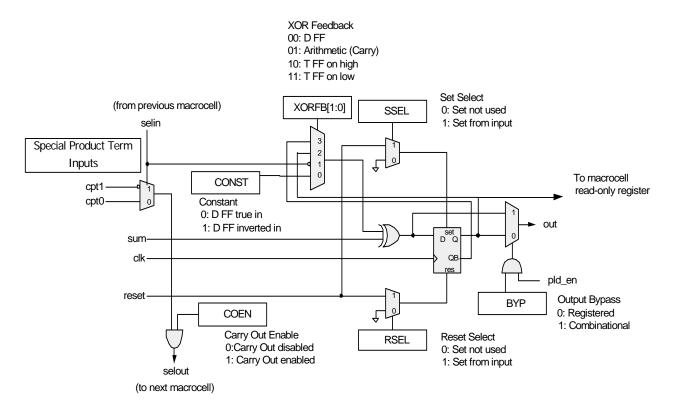

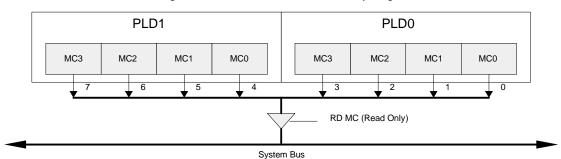

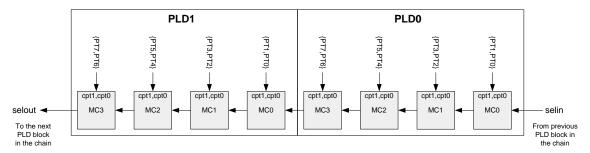

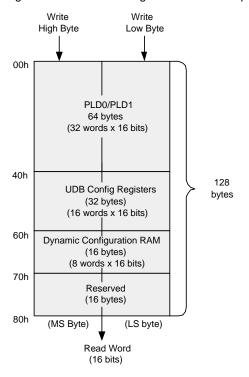

|         |        | 23.3.1 PLDs          |                                                         | 214             |

|         |        | 23.3.1.1             | PLD Macrocells                                          | 215             |

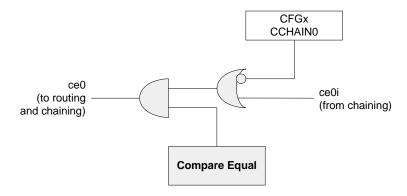

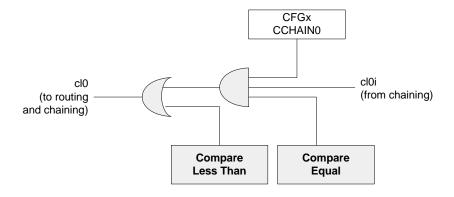

|         |        | 23.3.1.2             | PLD Carry Chain                                         | 217             |

|         |        | 23.3.1.3             | PLD Configuration                                       | 217             |

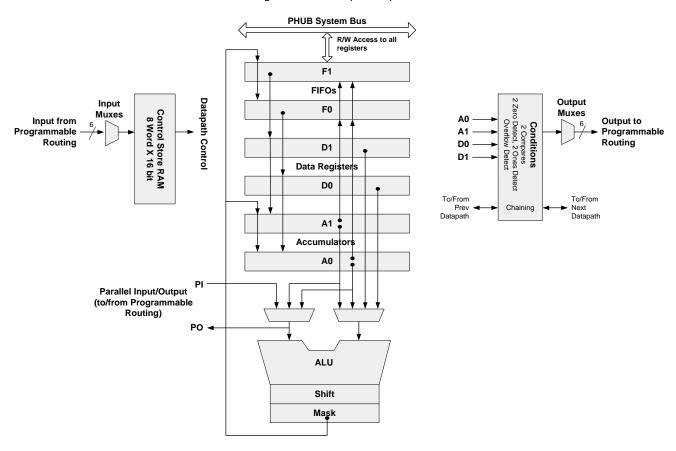

|         |        | 23.3.2 Datapa        | th                                                      | 217             |

|         |        | 23.3.2.1             | Overview                                                | 219             |

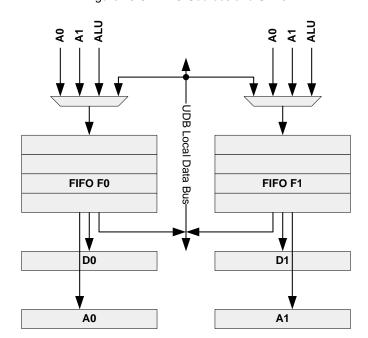

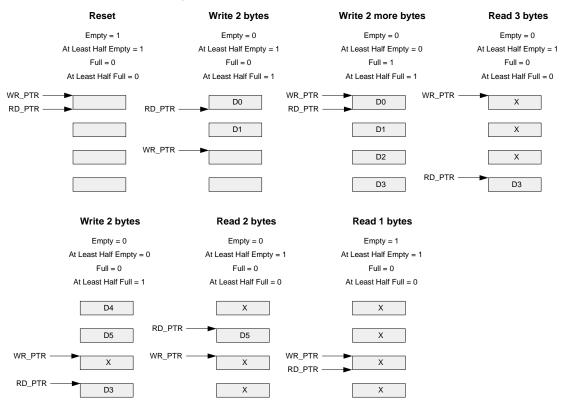

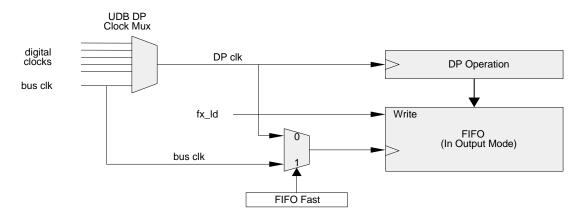

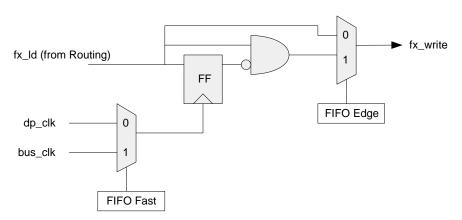

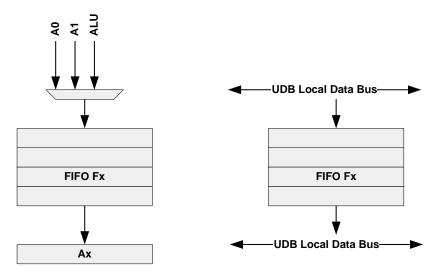

|         |        | 23.3.2.2             | Datapath FIFOs                                          | 220             |

|         |        | 23.3.2.3             | FIFO Status                                             |                 |

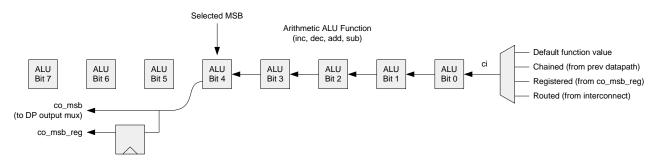

|         |        | 23.3.2.4             | Datapath ALU                                            | 227             |

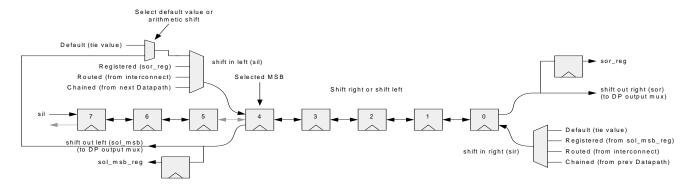

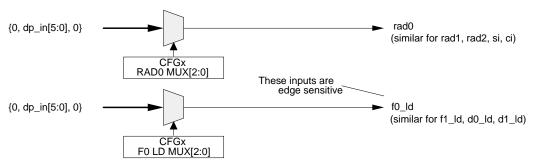

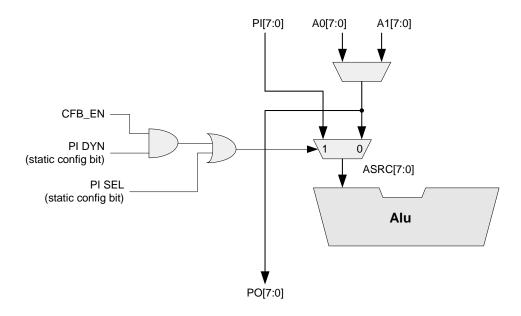

|         |        | 23.3.2.5             | Datapath Inputs and Multiplexing                        | 230             |

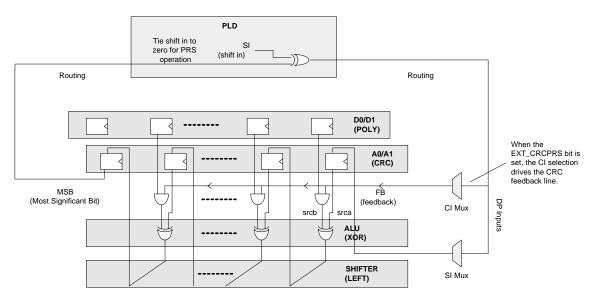

|         |        | 23.3.2.6             | CRC/PRS Support                                         | 230             |

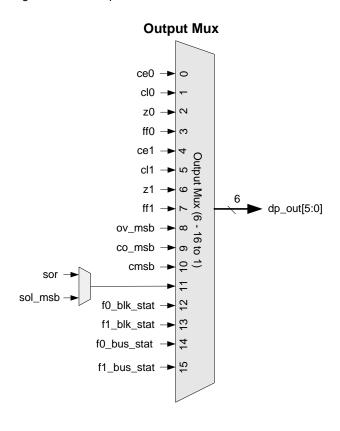

|         |        | 23.3.2.7             | Datapath Outputs and Multiplexing                       |                 |

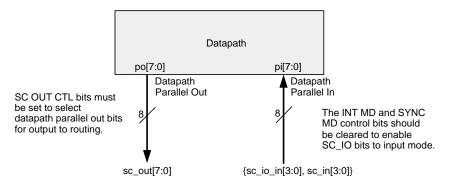

|         |        | 23.3.2.8             | Datapath Parallel Inputs and Outputs                    |                 |

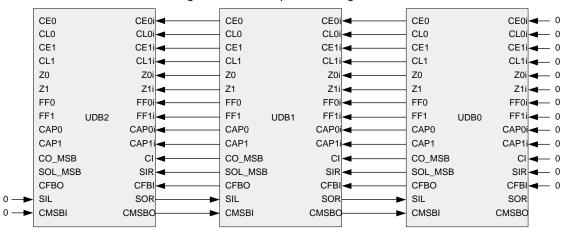

|         |        | 23.3.2.9             | Datapath Chaining                                       |                 |

|         |        | 23.3.2.10            | Dynamic Configuration RAM                               |                 |

|         |        |                      | and Control Module                                      |                 |

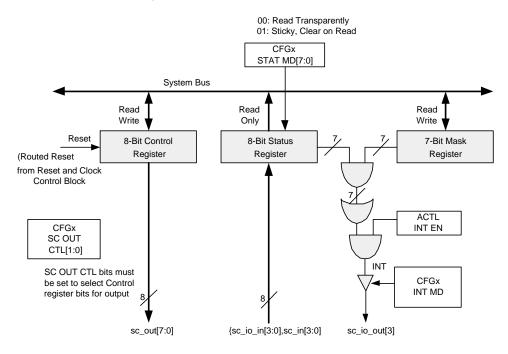

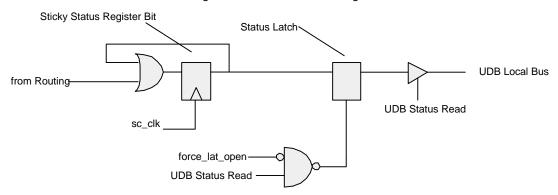

|         |        | 23.3.3.1             | Status and Control Mode                                 |                 |

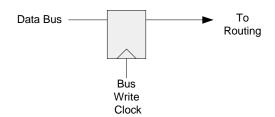

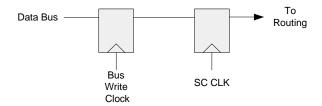

|         |        | 23.3.3.2             | Control Register Operation                              |                 |

|         |        | 23.3.3.3             | Parallel Input/Output Mode                              |                 |

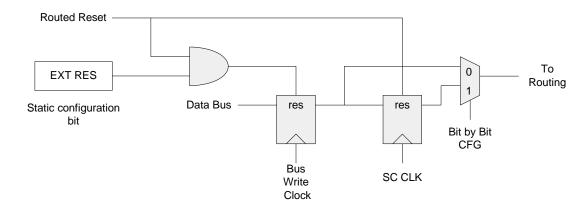

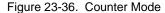

|         |        | 23.3.3.4             | Counter Mode                                            |                 |

|         |        | 23.3.3.5             | Sync Mode                                               |                 |

|         |        | 23.3.3.6             | Status and Control Clocking                             |                 |

|         |        | 23.3.3.7             | Auxiliary Control Register                              |                 |

|         |        | 23.3.3.8             | Status and Control Register Summary                     |                 |

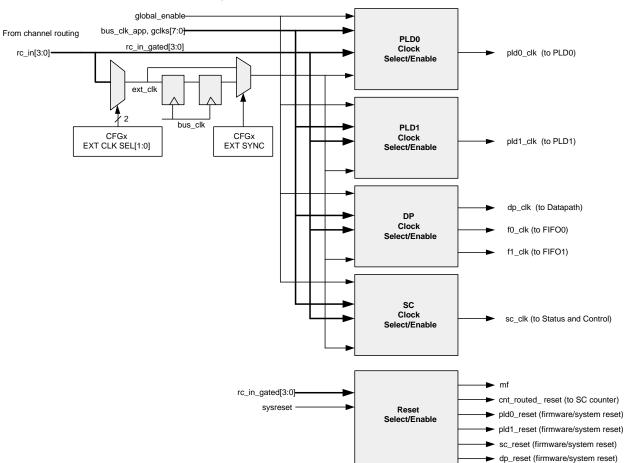

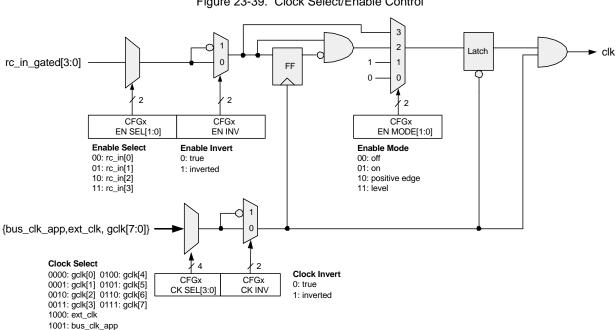

|         |        |                      | and Clock Control Module                                |                 |

|         |        | 23.3.4.1             | Clock Control                                           |                 |

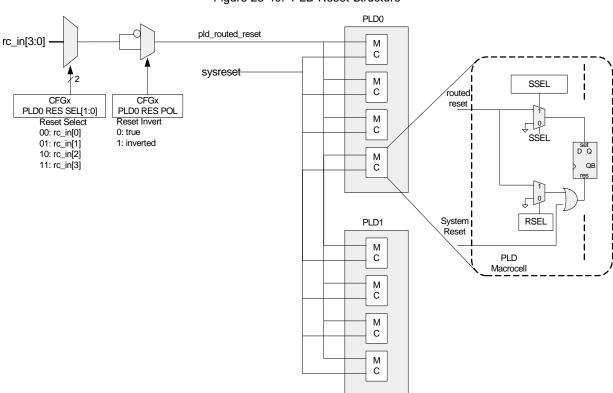

|         |        | 23.3.4.2             | Reset Control                                           | 247             |

|             |       | 23.3.4.3 UDB POR Initialization                                | 249 |

|-------------|-------|----------------------------------------------------------------|-----|

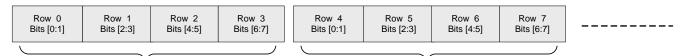

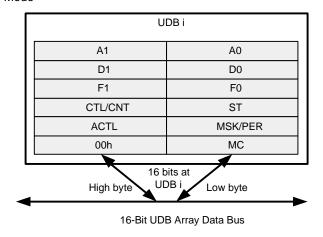

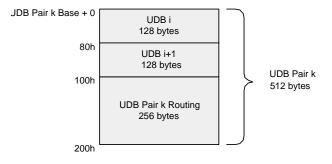

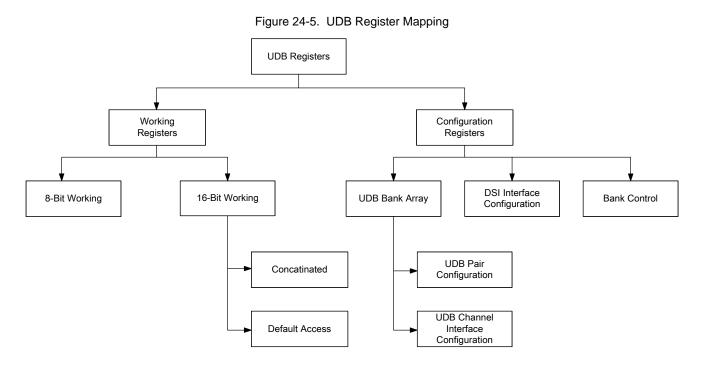

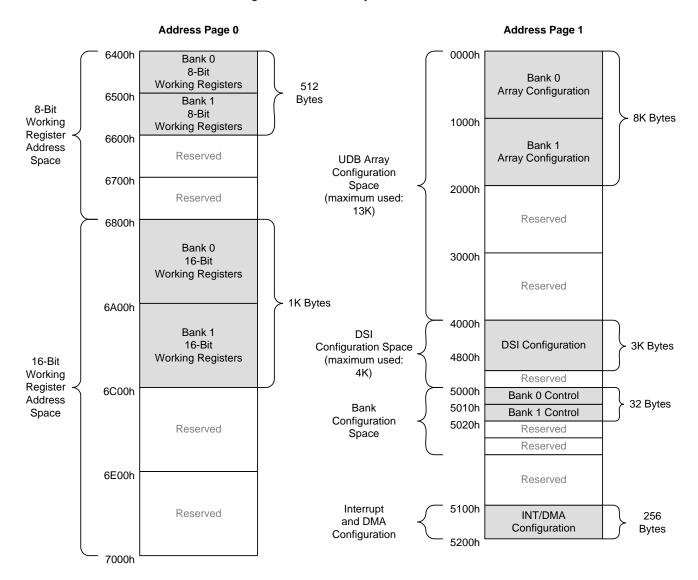

|             |       | 23.3.5 UDB Addressing                                          | 250 |

|             |       | 23.3.5.1 Working Register Address Space                        | 250 |

|             |       | 23.3.5.2 Configuration Register Address Space                  |     |

|             |       | 23.3.5.3 UDB Configuration Address Space                       |     |

|             |       | 23.3.5.4 Routing Configuration Address Space                   |     |

|             |       | 23.3.6 System Bus Access Coherency                             |     |

|             |       | 23.3.6.1 Simultaneous System Bus Access                        |     |

|             |       | 23.3.6.2 Coherent Accumulator Access (Atomic Reads and Writes) |     |

|             | 23.4  | UDB Working Register Reference                                 |     |

| •           |       |                                                                |     |

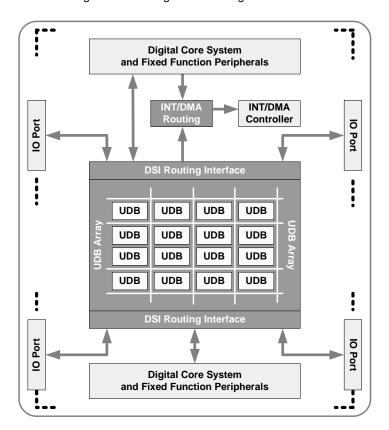

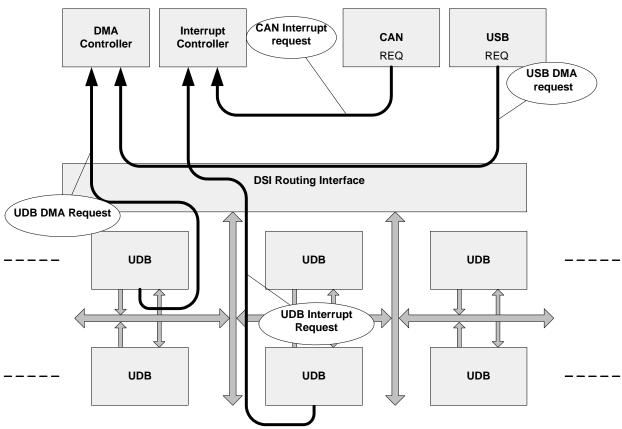

| 24.         | ODB / | Array and Digital System Interconnect                          | 255 |

|             | 24.1  | Features                                                       |     |

|             | 24.2  | Block Diagram                                                  | 255 |

|             | 24.3  | How It Works                                                   | 256 |

|             | 24.4  | UDB Array System Interface                                     | 258 |

|             |       | 24.4.1 UDB Array POR Initialization                            | 258 |

|             |       | 24.4.2 UDB POR Configuration Sequence                          | 259 |

|             |       | 24.4.2.1 Quadrant Route Disable                                | 260 |

|             |       | 24.4.3 UDB Sleep and Power Control                             | 260 |

|             |       | 24.4.4 UDB Register References and Address Mapping             | 260 |

| ٥.          | 0     | allan Anag Naturanis (CANI)                                    | 000 |

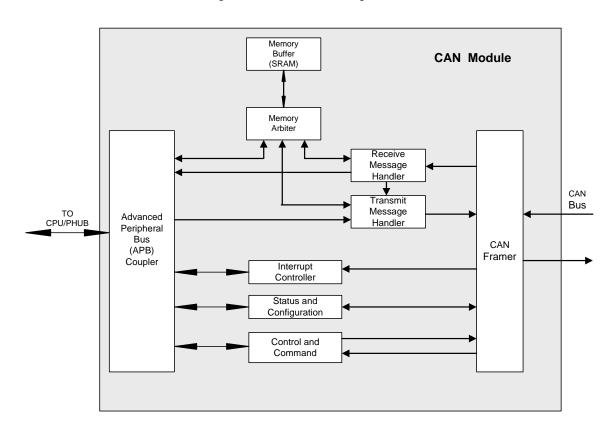

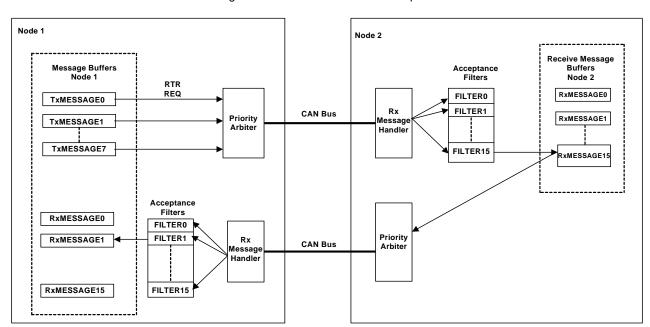

| <b>2</b> 5. | Contr | oller Area Network (CAN)                                       | 263 |

|             | 25.1  | Features                                                       |     |

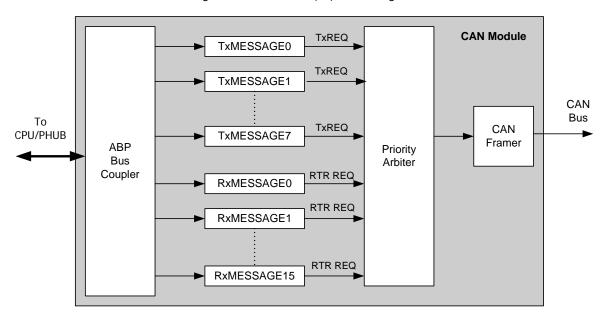

|             | 25.2  | Block Diagram                                                  |     |

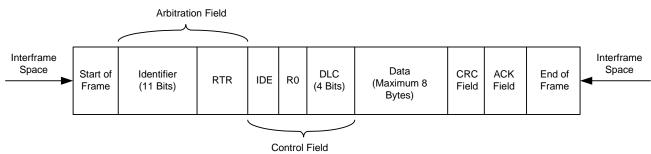

|             | 25.3  | CAN Message Frames                                             | 264 |

|             |       | 25.3.1 Data Frames                                             | 264 |

|             |       | 25.3.1.1 Standard Data Frame                                   | 264 |

|             |       | 25.3.1.2 Extended Data Frame                                   | 265 |

|             |       | 25.3.2 Remote Frame                                            | 266 |

|             |       | 25.3.3 Error Frame                                             | 266 |

|             |       | 25.3.4 Overload Frame                                          | 266 |

|             | 25.4  | Transmitting Messages in CAN                                   |     |

|             |       | 25.4.1 Message Arbitration                                     |     |

|             |       | 25.4.2 Message Transmit Process                                |     |

|             |       | 25.4.3 Message Abort                                           |     |

|             |       | 25.4.4 Transmitting Extended Data Frames                       |     |

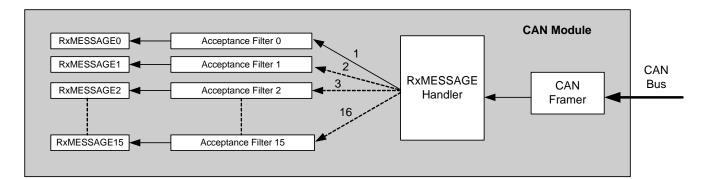

|             | 25.5  | Receiving Messages in CAN                                      |     |

|             | 20.0  | 25.5.1 Message Receive Process                                 |     |

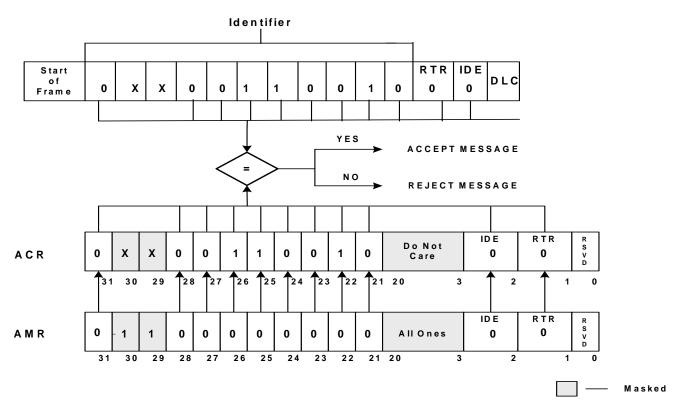

|             |       | 25.5.2 Acceptance Filter                                       |     |

|             |       | 25.5.2.1 Example                                               |     |

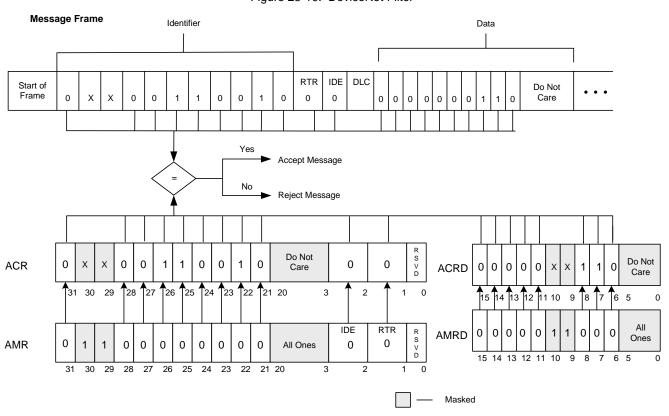

|             |       | 25.5.3 DeviceNet Filtering                                     |     |

|             |       | 25.5.4 Filtering of Extended Data Frames                       |     |

|             |       | 25.5.5 Receiver Message Buffer Linking                         |     |

|             | 25.6  | Remote Frames                                                  |     |

|             | 23.0  | 25.6.1 Transmitting a Remote Frame by the Requesting Node      |     |

|             |       |                                                                |     |

|             |       | 25.6.2 Receiving a Remote Frame                                |     |

|             |       | 25.6.3 RTR Auto Reply                                          |     |

|             | 05.7  | 25.6.4 Remote Frames in Extended Format                        |     |

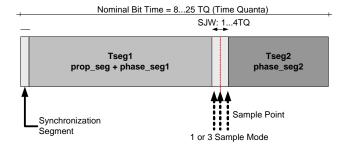

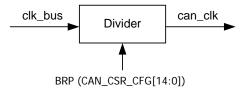

|             | 25.7  | Bit Time Configuration                                         |     |

|             |       | 25.7.1 Allowable Bit Rates and System Clock (CLK_BUS)          |     |

|             |       | 25.7.2 Setting Bit Rate TSEG1 and TSEG2                        |     |

|             |       | 25.7.2.1 Example                                               | 276 |

|     | 25.8  | Error Handling an | d Interrupts in CAN        | 276 |

|-----|-------|-------------------|----------------------------|-----|

|     |       | 25.8.1 Types      | of Errors                  | 276 |

|     |       | 25.8.1.1          | BIT Error                  | 276 |

|     |       | 25.8.1.2          | FORM Error                 | 276 |

|     |       | 25.8.1.3          | ACKNOWLEDGE Error          | 276 |

|     |       | 25.8.1.4          | CRC Error                  | 276 |

|     |       | 25.8.1.5          | STUFF Error                | 277 |

|     |       | 25.8.2 Error S    | tates in CAN               | 277 |

|     |       |                   | ot Sources in CAN          |     |

|     | 25.9  | Operating Modes   | in CAN                     | 278 |

|     |       |                   | Only Mode                  |     |

|     |       |                   | op Mode                    |     |

| 26  | HED   |                   | •                          | 279 |

| 20. | USB   |                   |                            | _   |

|     | 26.1  |                   |                            |     |

|     | 26.2  | · ·               |                            |     |

|     |       |                   | nterface Engine (SIE)      |     |

|     |       |                   |                            |     |

|     |       | 26.2.2.1          | SIE Interface Module       |     |

|     |       | 26.2.2.2          | CPU Interface Block        |     |

|     |       | 26.2.2.3          | Memory Interface           |     |

|     |       | 26.2.2.4          | DMA Interface              |     |

|     |       | 26.2.2.5          | Arbiter Logic              |     |

|     |       | 26.2.2.6          | Synchronization Block      |     |

|     | 26.3  |                   |                            |     |

|     |       |                   | ing Frequency              |     |

|     |       | •                 | ing Voltage                |     |

|     |       |                   | eiver                      |     |

|     |       | •                 | nts                        |     |

|     |       |                   | er Types                   |     |

|     |       |                   | ots                        |     |

|     | 26.4  | •                 | Modes                      |     |

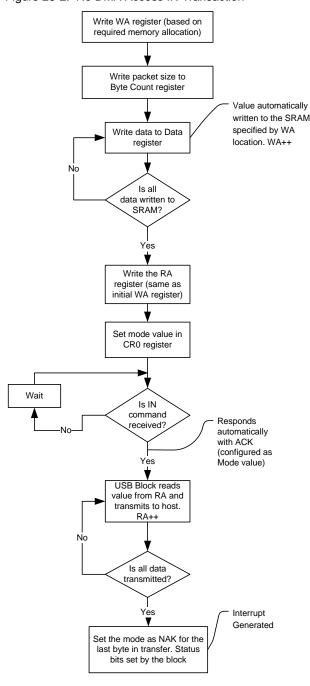

|     |       |                   | nd Forward Mode            |     |

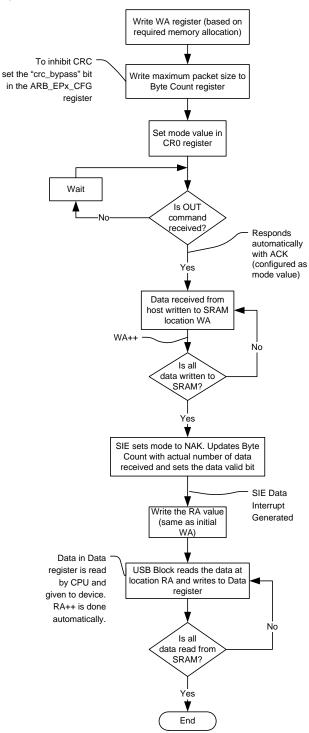

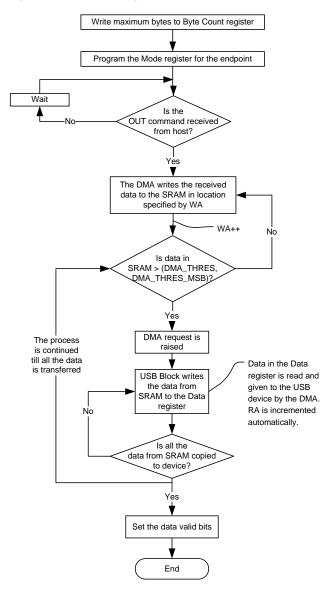

|     |       | 26.4.1.1          | No DMA Access              |     |

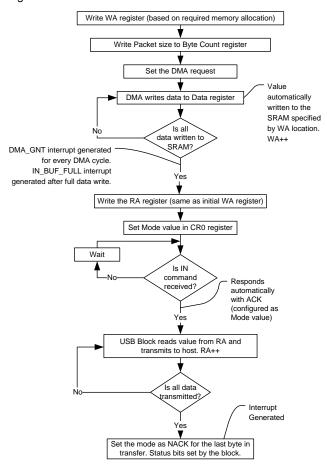

|     |       | 26.4.1.2          | Manual DMA Access          |     |

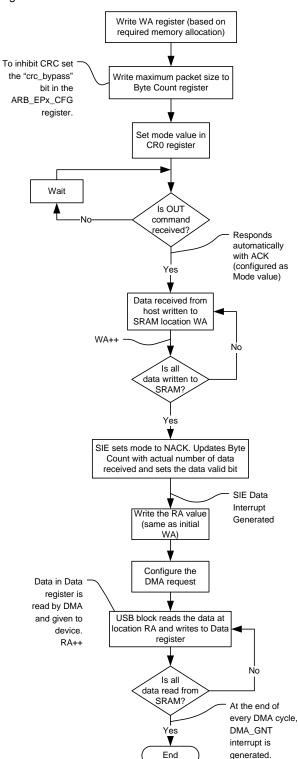

|     |       |                   | rough Mode                 |     |

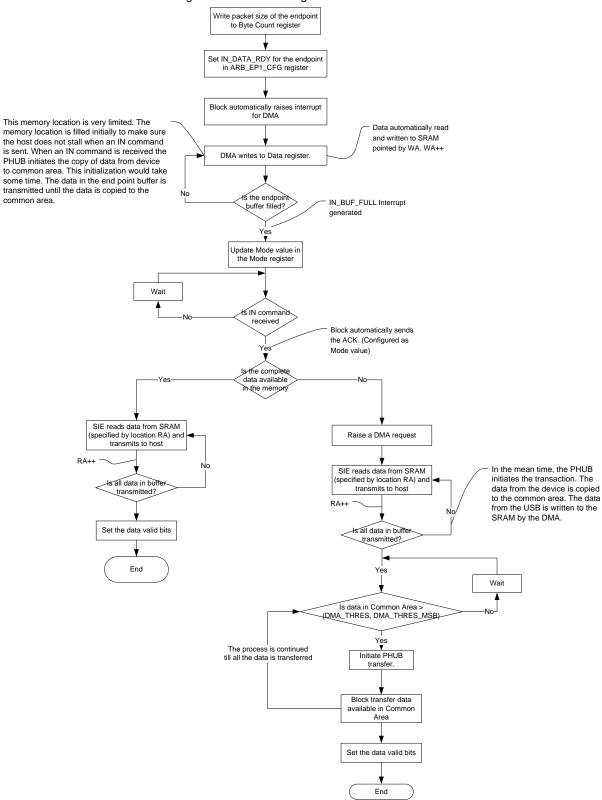

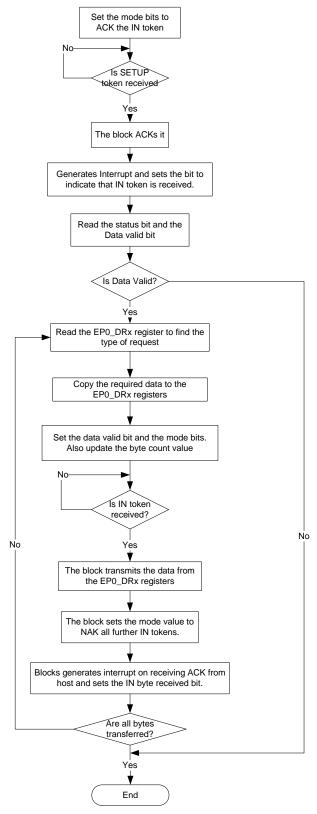

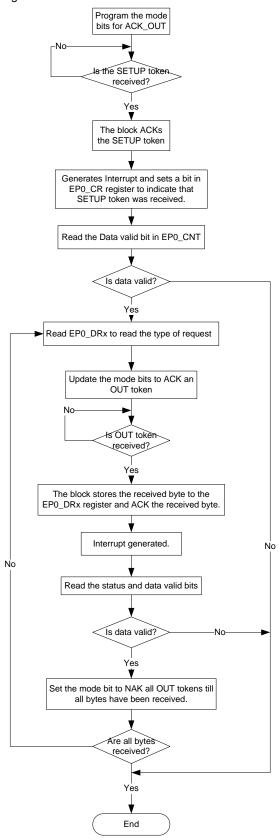

|     |       |                   | Endpoint Logical Transfer  |     |

|     | 26.5  |                   | I/O Modes                  |     |

|     | 26.6  | Register List     |                            | 293 |

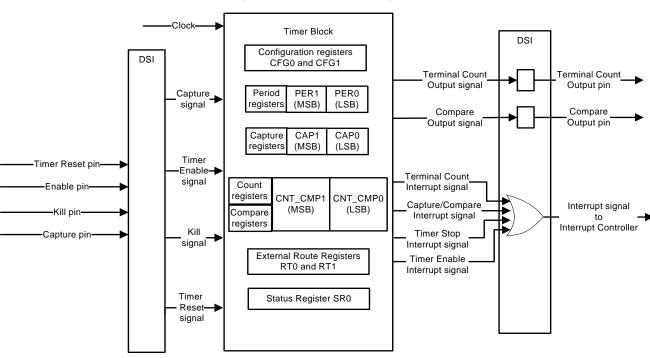

| 27. | Timer | , Counter, and    | PWM                        | 295 |

|     | 27.1  | •                 |                            | 295 |

|     | 27.2  |                   |                            |     |

|     | 27.3  | _                 |                            |     |

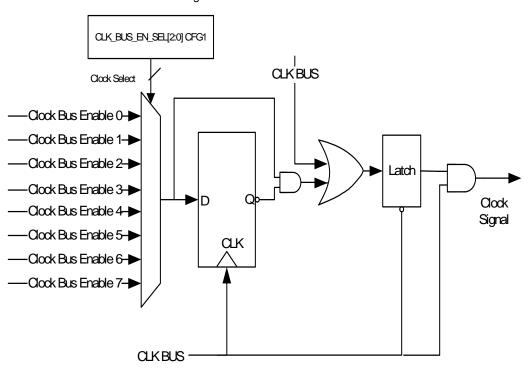

|     | 27.0  |                   | Selection                  |     |

|     |       |                   | ng and Disabling Block     |     |

|     |       |                   | ignal Characteristics      |     |

|     |       | 27.3.3.1          | Enable Signal              |     |

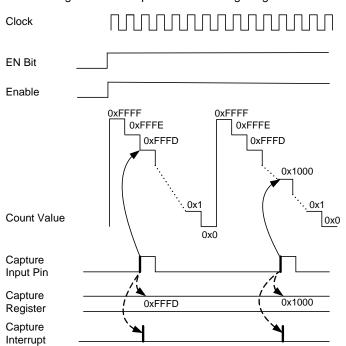

|     |       | 27.3.3.2          | Capture Signal             |     |

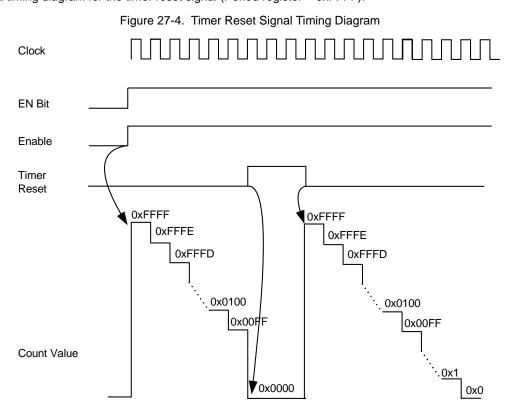

|     |       | 27.3.3.3          | Timer Reset Signal         |     |

|     |       | 27.3.3.4          | Kill Signal                |     |

|     |       |                   | ing Modes                  |     |

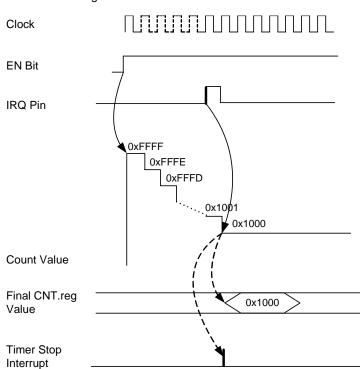

|     |       | -                 | Timer Mode – Free Run Mode |     |

|     |                  | 27.3.4.2          | Gated Timer Mode                  |     |

|-----|------------------|-------------------|-----------------------------------|-----|

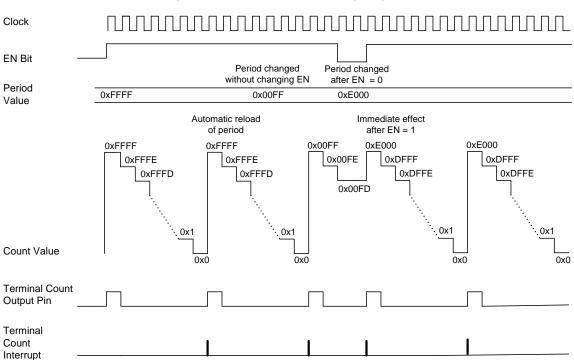

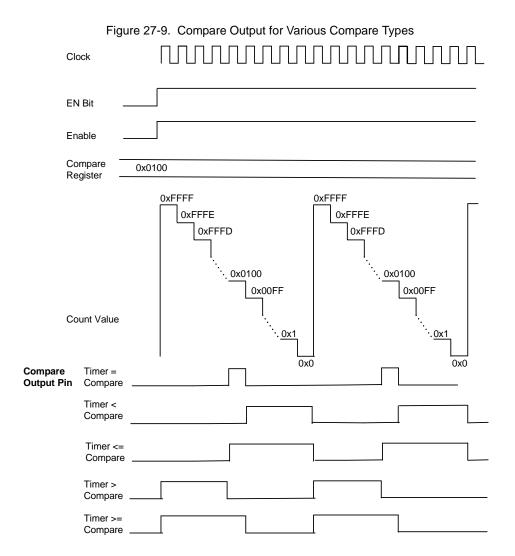

|     |                  | 27.3.4.3          | Pulse-width Modulator Mode        | 306 |

|     |                  | 27.3.4.4          | One Shot Mode                     | 309 |

|     |                  | 27.3.5 Interrup   | t Enabling                        | 309 |

|     |                  | 27.3.6 Sleep M    | lode Behavior                     | 310 |

|     | 27.4             |                   |                                   |     |

| 28. | I <sup>2</sup> C |                   |                                   | 311 |

|     | 28.1             | Features          |                                   | 311 |

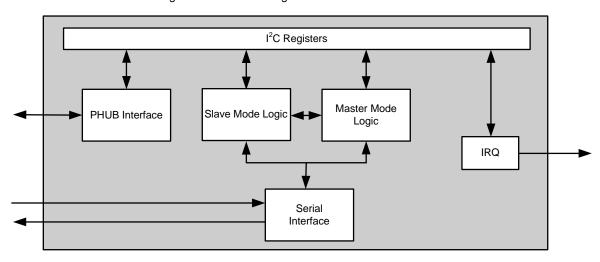

|     | 28.2             |                   |                                   |     |

|     | 28.3             |                   | nation                            |     |

|     | _0.0             |                   | Description                       |     |

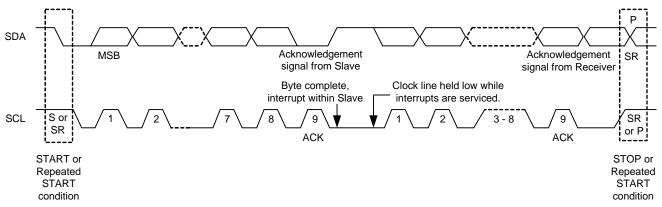

|     |                  |                   | I <sup>2</sup> C Data Transfer    |     |

|     | 28.4             |                   | - C Data Transion                 |     |

|     | 20.1             |                   | lling (Clock Stretching)          |     |

|     |                  |                   | Management Bus                    |     |

|     |                  |                   | nections                          |     |

|     |                  |                   | rrupts                            |     |

|     |                  |                   | by Registers                      |     |

|     |                  |                   | ng the I <sup>2</sup> C Interface |     |

|     |                  | 28.4.6.1          | Slave Mode                        |     |

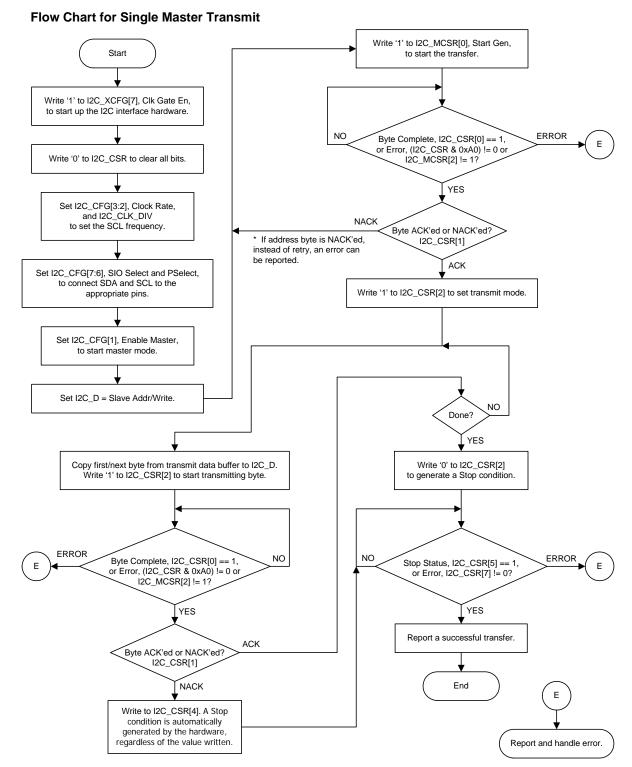

|     |                  | 28.4.6.2          | Master Mode                       |     |

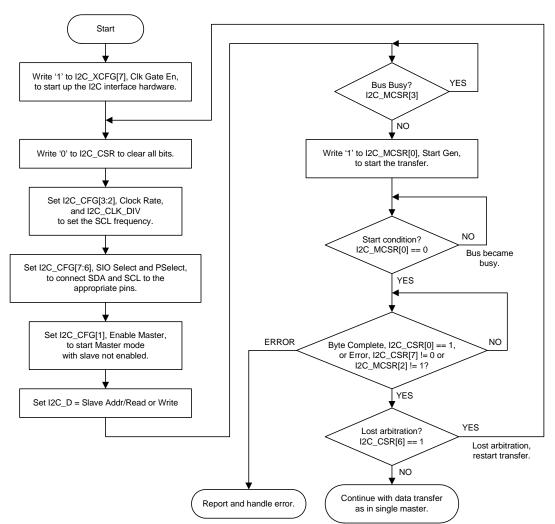

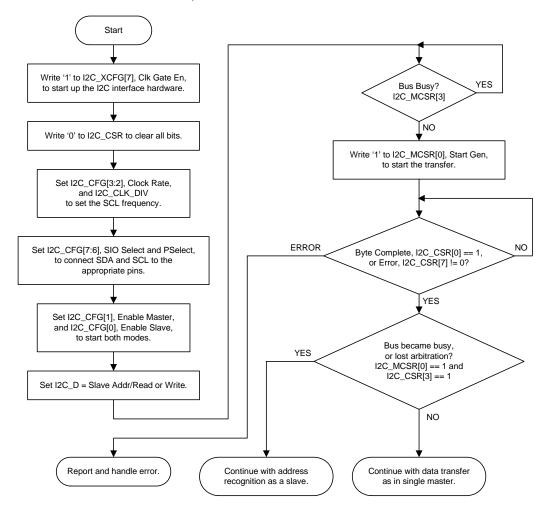

|     |                  | 28.4.6.3          | Multi-Master Mode                 |     |

|     | 20.5             |                   | s Compare                         |     |

|     |                  |                   |                                   |     |

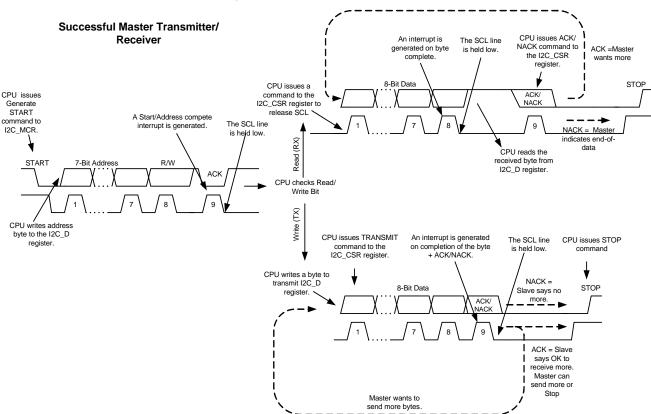

|     | 28.7             |                   | fer Examples                      |     |

|     | 20.7             |                   | eceive                            |     |

|     |                  |                   | ransmit                           |     |

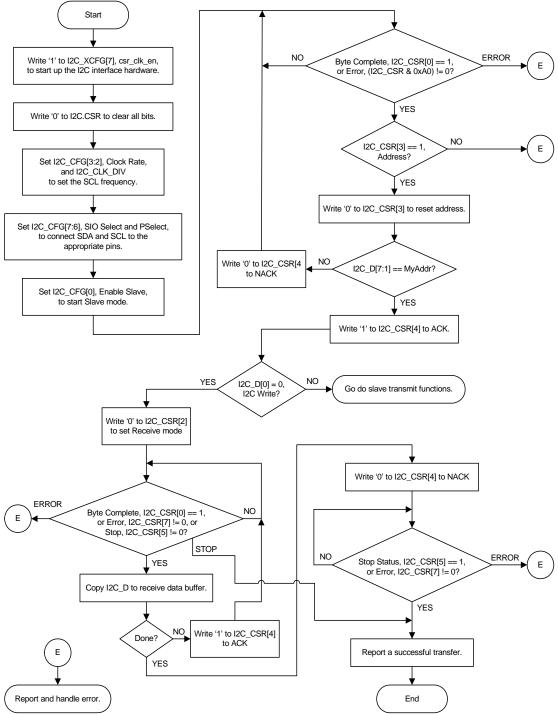

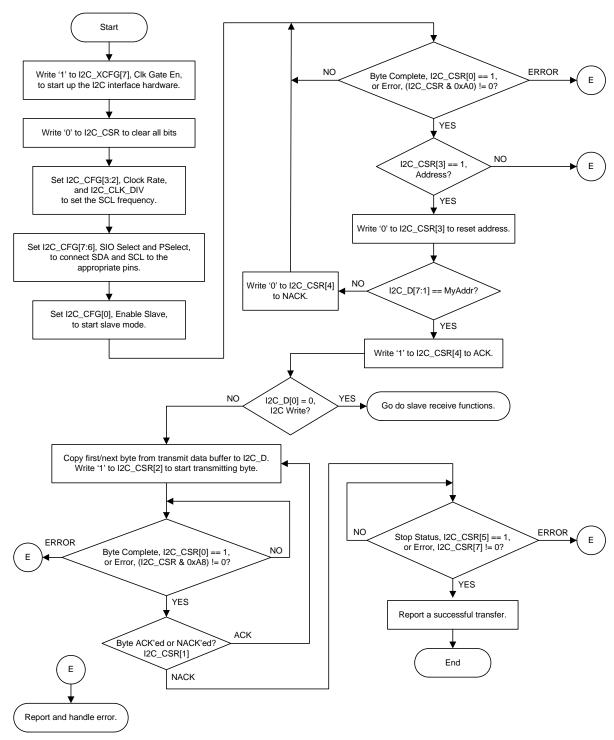

|     | 20.0             |                   | sfer Examples                     |     |

|     | 28.8             |                   |                                   |     |

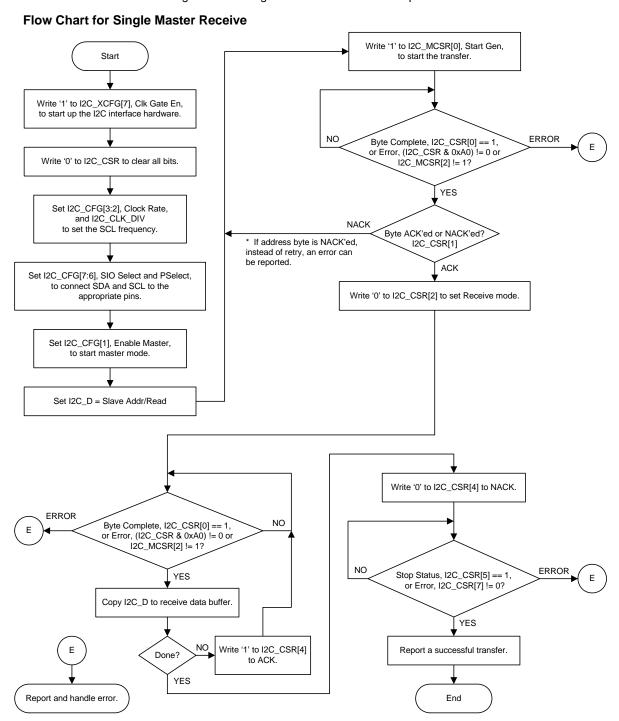

|     |                  |                   | Master Receive                    |     |

|     | 00.0             |                   | Master Transmit                   |     |

|     | 28.9             |                   | Transfer Examples                 |     |

|     |                  |                   | aster, Slave Not Enabled          |     |

|     |                  |                   | aster, Slave Enabled              |     |

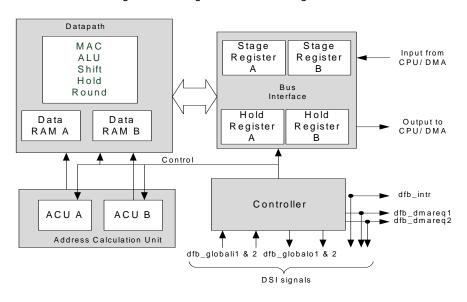

| 29. | _                | l Filter Block (D | •                                 | 327 |

|     | 29.1             |                   |                                   |     |

|     | 29.2             |                   |                                   |     |

|     | 29.3             |                   |                                   |     |

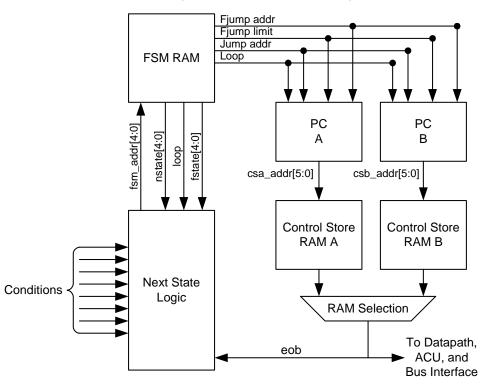

|     |                  |                   | er                                |     |

|     |                  | 29.3.1.1          | FSM RAM                           |     |

|     |                  | 29.3.1.2          | Program Counter                   |     |

|     |                  | 29.3.1.3          | Control Store                     |     |

|     |                  | 29.3.1.4          | Next State Decoder                |     |

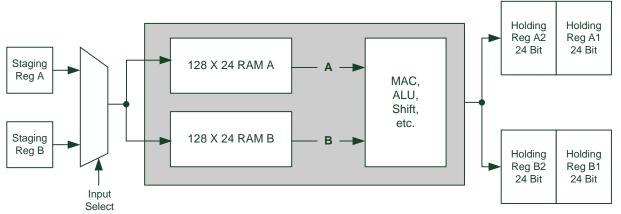

|     |                  | 29.3.2 Datapat    |                                   |     |

|     |                  | 29.3.2.1          | MAC                               |     |

|     |                  | 29.3.2.2          | ALU                               | 332 |

|     |                  | 29.3.2.3          | Shifter and Rounder               | 332 |

|     |                  | 29.3.3 Address    | Calculation Unit                  | 333 |

|     |                  |                   | erface and Register Descriptions  |     |

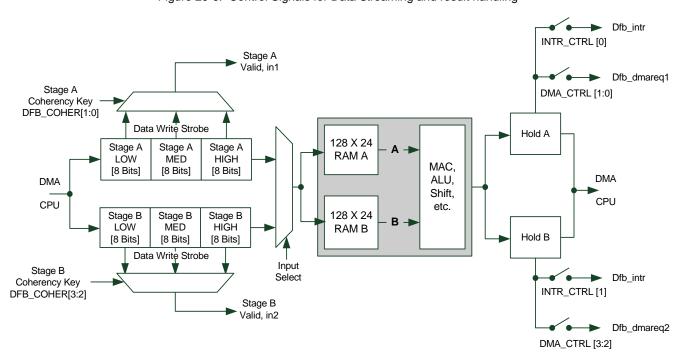

|     |                  | 29.3.4.1          | Streaming Mode                    |     |

|     |                  | 29.3.4.2          | Block Transfer Modes              |     |

|     |                  | 29.3.4.3          | Result Handling                   |     |

|     |                  |                   | <del>-</del>                      |     |

|         |                                                                     | 29.3.4.4 Data Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                 |

|---------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|         |                                                                     | 29.3.4.5 DMA and Semaphores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

|         |                                                                     | 29.3.4.6 DSI Routed Inputs and Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

|         |                                                                     | DFB Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |

|         | 29.5                                                                | Usage Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 341                                                             |

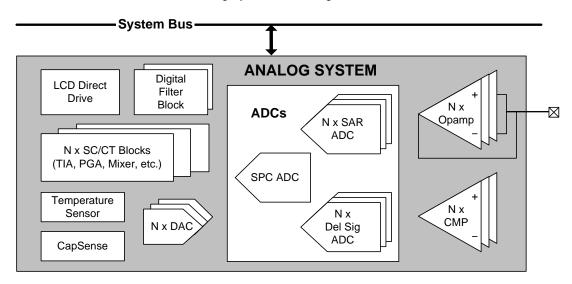

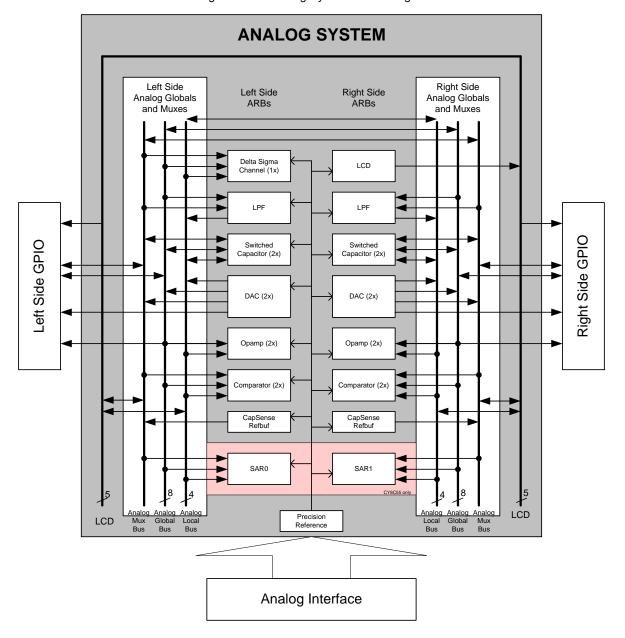

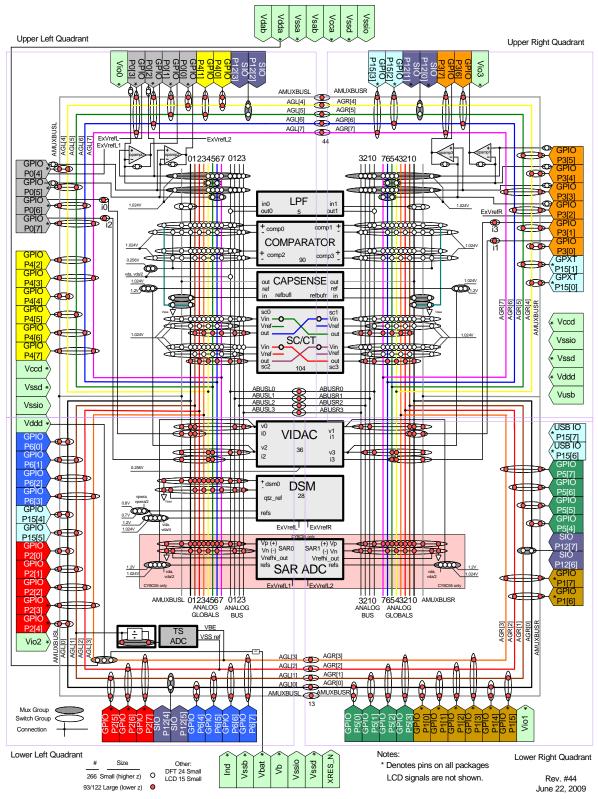

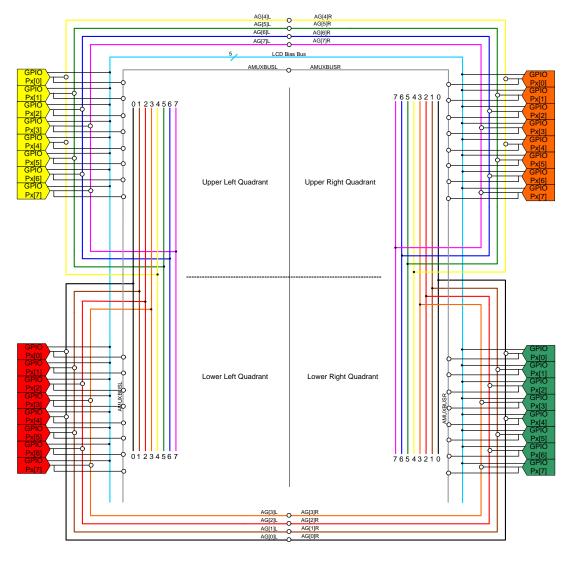

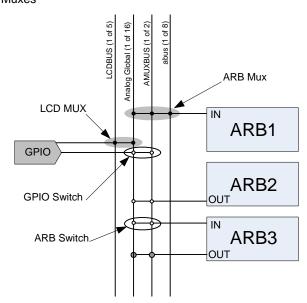

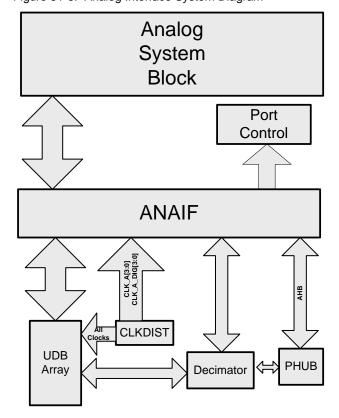

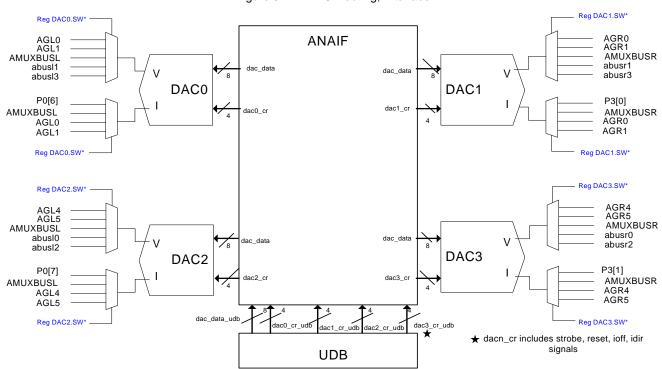

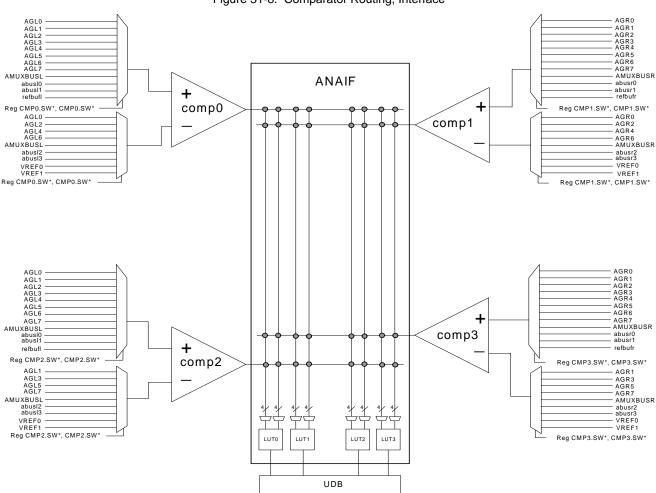

| Section |                                                                     | alog System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 343                                                             |

|         | Top I                                                               | _evel Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 343                                                             |

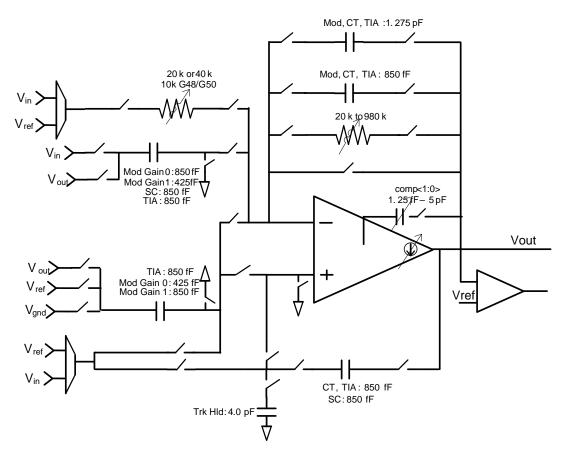

| 30.     | Switc                                                               | hed Capacitor/Continuous Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 345                                                             |

|         | 30.1                                                                | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |

|         | 30.2                                                                | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 345                                                             |

|         | 30.3                                                                | How it Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |

|         |                                                                     | 30.3.1 Operational Mode of Block is Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                 |

|         | 30.4                                                                | Naked Opamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

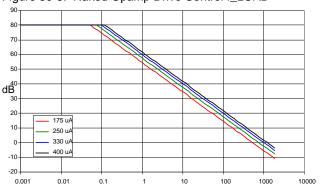

|         |                                                                     | 30.4.1 Bandwidth/Stability Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

|         |                                                                     | 30.4.1.1 BIAS_CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

|         |                                                                     | 30.4.1.2 SC_COMP[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

|         |                                                                     | 30.4.1.3 SC_REDC[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

|         | 30.5                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

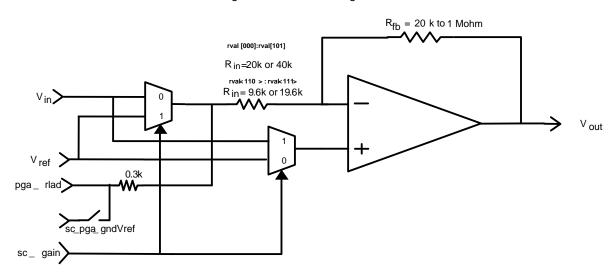

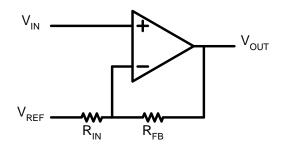

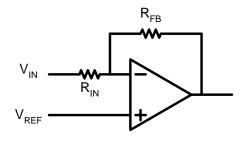

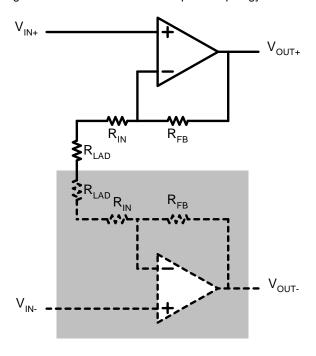

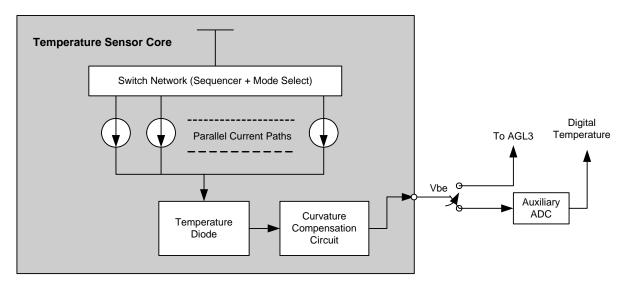

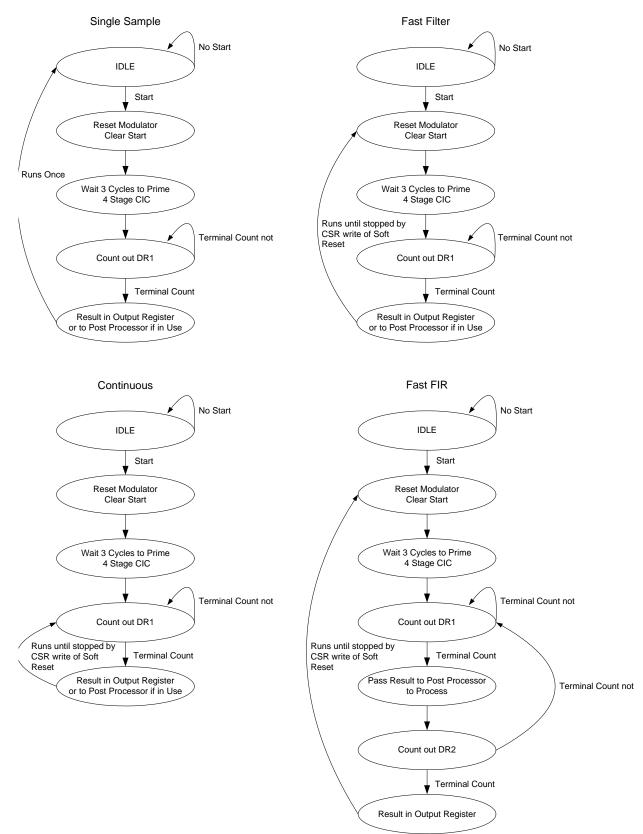

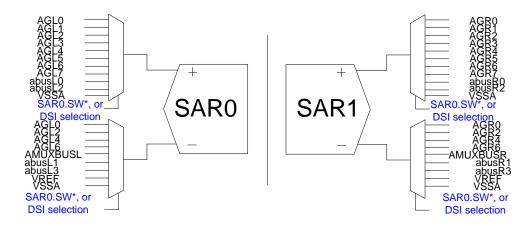

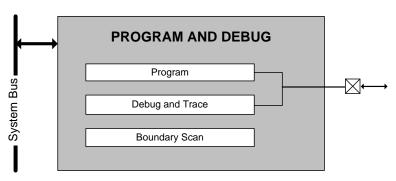

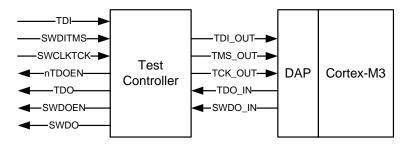

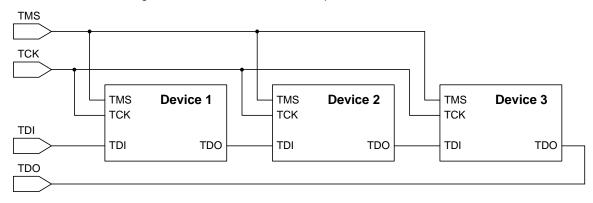

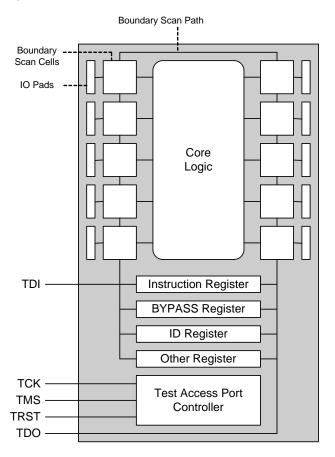

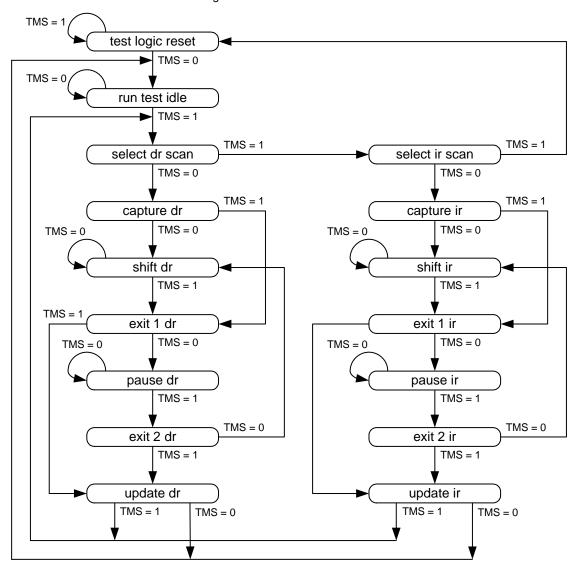

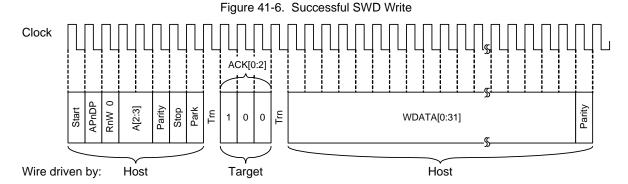

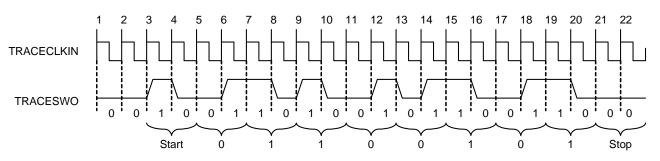

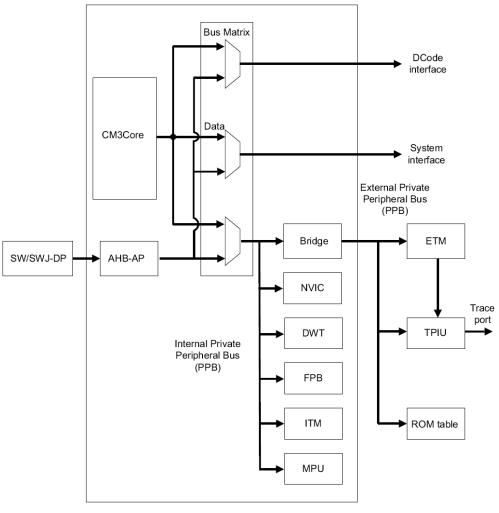

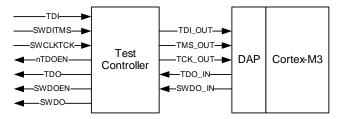

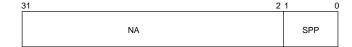

|         |                                                                     | Continuous Time Programmable Gain Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |